摘要:以STM32F103作为微处理器,设计了一个低成本的无线WiFi音乐播放系统,结合接收WiFi数据的WM-G-MR-08(wm631)模块和VS1003B音频解码器实现了MP3音乐播放。基于An

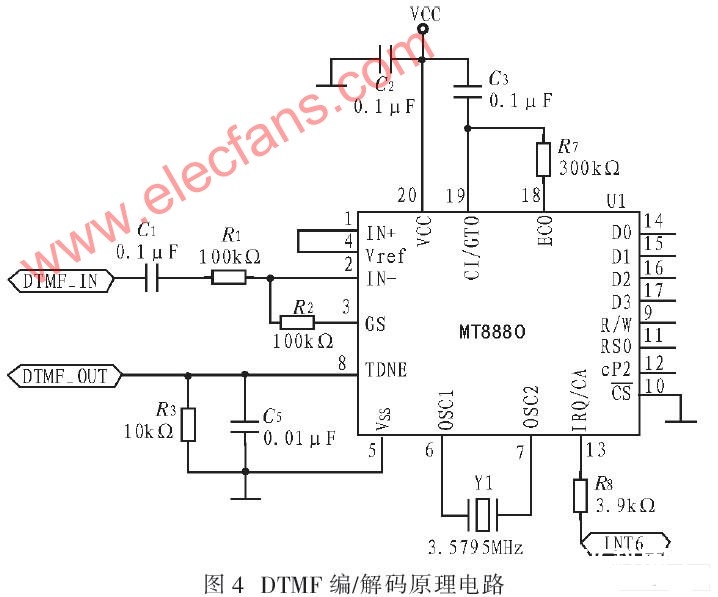

DTMF编/解码器选用MT8880。MT8880C是一个带有呼叫处理滤波器的单片DTMF信号收发器。该器件采用低功耗、高稳定性的ISO-CMOS技术,内置1个带有可变增益的内部放大器的高性能接收器,1

185-265VDC输入、60W多路输出电源电路图44所示的多输出电源电路常用于使用了大容量记录硬盘的高档机顶盒和有线电视解码器等应用。在输入电压范围为185到265VAC时,电源提供45W(连续)/

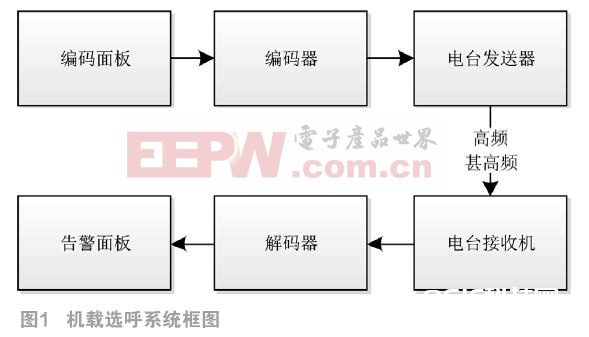

针对机载电子设备综合化的需求,本文以DSP处理器为核心实现了机载选择呼叫数字化解码器系统,利用数字信号处理算法设计解码方法及通过状态机方法设计解码控制流程,完成解码纯软件化实现。通过在高强度噪声环境下

同步时钟信号是分布式录波器系统任务顺利完成的关键。介绍一种利用可编程CPLD器件实现性能优良的分布式同步信号源。通过高度集成,将IRIG-B(DC)解码器以及系统的各种同步逻辑电路集成在一个MAXII

为满足SoC中JPEG静止图像实时解压缩要求,在完成JPEG解码器C语言建模的基础上,采用自顶向下的设计方法,完成了JPEG Baseline解码器设计,并在FPGA开发板上验证了设计结果。该设计与A