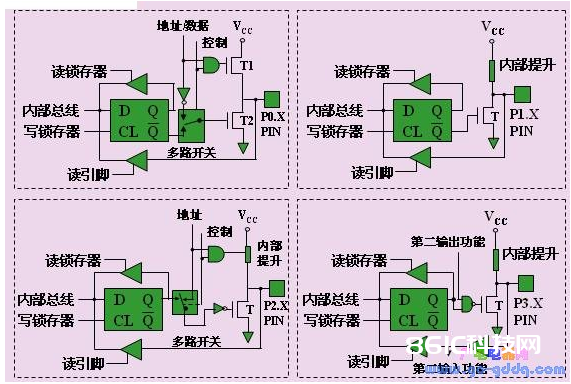

MCS-51单片机四个双向8位IO口的工作原理解析-P0~P3的口锁存器结构都是一样的,P0~P3口的每一位口锁存器都是一个D触发器,复位以后的初态为1。但输入缓冲器和输出驱动器的结构有差别。CPU通过内部总线把数据写入口锁存器。

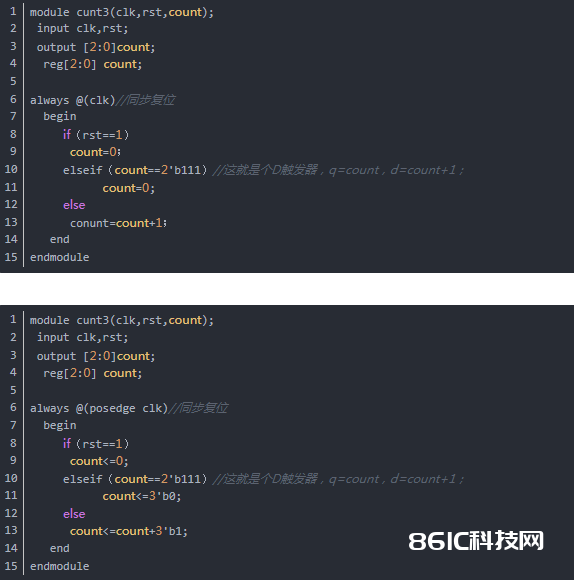

基于FPGA的同步复位的3位计数器设计-分析:首先,我们可以看到有哪些信号。复位rst 、计数器3位的、时钟信号。(用到2路选择器。复位和不复位)

其次,怎样实现,一个时钟过来,记一次数就是加一次,保存(用到D触发器),满之后为0;

关于FPGA基础知识的一些科普问答-同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。改变后的状态将一直保持到下一个时 钟脉冲的到来,此时无论外部输入 x有无变化,状态表中的每个状态都是稳定的。 异步时序逻辑电路的特点:电路中除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件,电路中没有统一的时钟,电路状态的改变由外部输入的 变化直接引起。

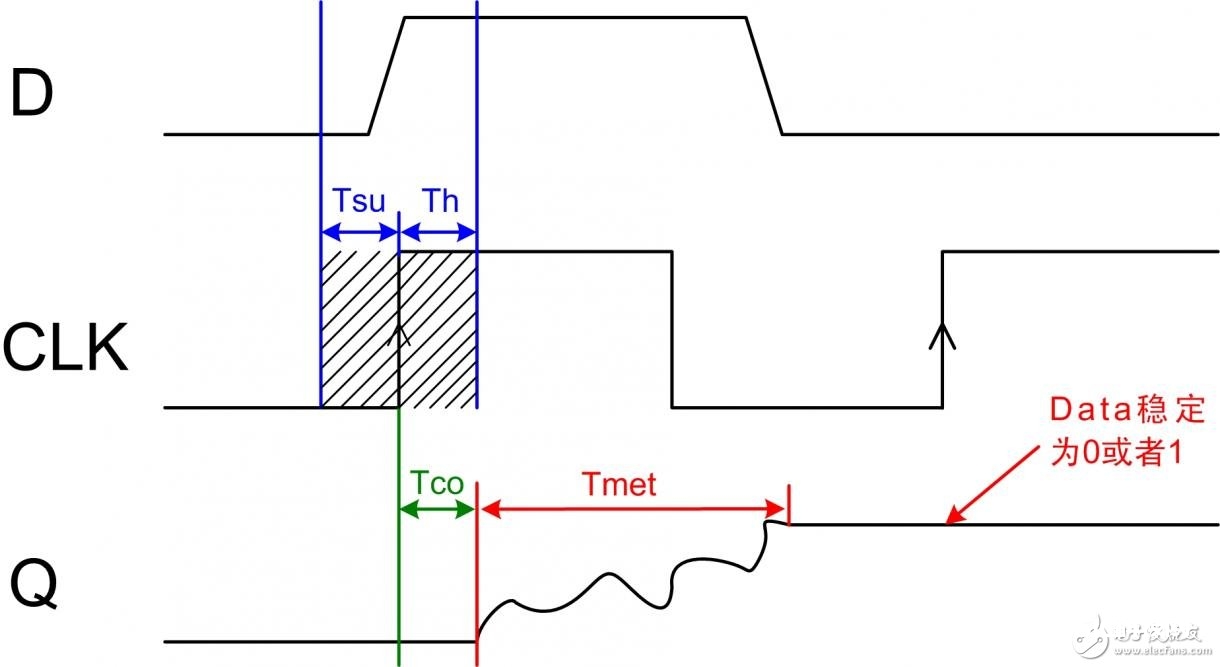

FPGA系统中三种方式减少亚稳态的产生-在FPGA系统中,如果数据传输中不满足触发器的Tsu和Th不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端在0和1之间处于振荡状态,而不是等于数据输入端D的值。