利用半拍错位同步法消除异步电路的亚稳态-当今的数字系统往往是围绕CPLD/ FPGA 进行设计的, 首选的方案是采用同步时序电路设计 , 也称作单时钟系统, 电路中所有触发器的时钟输入端共享同一个时钟, 每个触发器的状态变化都是在时钟的上升沿( 或下降沿) 完成的, 与时钟脉冲信号同步。

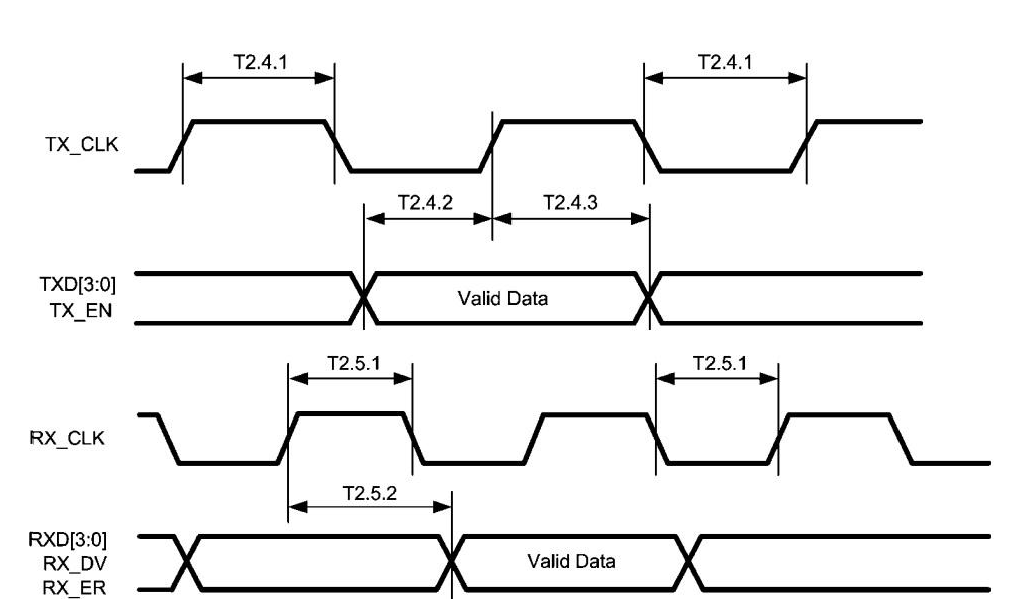

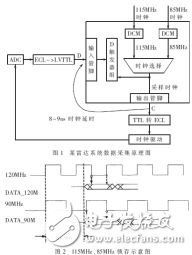

基于FPGA的自适应同步器电路设计详解- 在许多高速数据采集系统中,数据正确锁存是设计者必须要面对的问题。特别是在内部时钟与外部时钟采用同一个时钟源的基于FPGA的高速数据采集系统中,由于走线延时、器件延时、FPGA输入管脚延时,导致FPGA输入数据与FPGA内部时钟的相对相位关系不确定;在时钟频率可变的情况下,相对相位关系还会随频率变化。在FPGA内部一般采用D触发器实现对输入数据的采样。为了避免亚稳态 ,D触发器要求输入数据相对时钟沿满足一定的建立、保持时间,即输入数据与FPGA内部时钟要满足一定的相位关系。由于输入数据与采样时钟相对相位的不确定性,就有可能不满足FPGA内部D触发器的建立、保持时间,出现亚稳态。针对上述情况,本文给出在FPGA中可以自适应地选择时钟上升沿或下降沿采样的自适应同步器电路设计。该电路能够检测锁存时钟上升沿与输入数据

零基础学FPGA设计难吗 FPGA基本知识介绍-很多初学者觉得学FPGA很难,需要很多的基础,得懂VERILOG设计、会画原理图,会画PCB,还有各种各样不同接口,是这样吗?首先看数字电路,了解什么是与或非,各种触发器,各种逻辑门,注意!了解即可,但是是怎么工作的一定要透彻透彻透彻透彻!

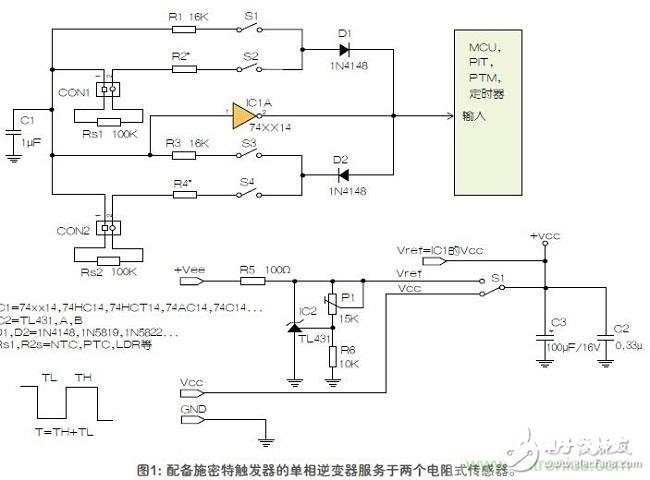

施密特触发器与电阻式传感器之间的绝密关系-在我们周围,许多捕捉信息的传感器都具有电阻性,如NTC传感器、PTC传感器、LDR传感器和接触式传感器等。如果将这类传感器的电阻转换为频率或脉冲持续时间,那么在不需要模拟数字转换器(ADC)的情况下,利用大部分的微控制器(MCU)就可以对这些参数进行测量。

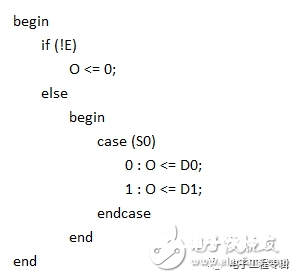

带异步清0、异步置1的D触发器moduleDFF1(q,qn,d,clk,set,reset);inputd,clk,set,reset;outputq,qn;regq,qn;always@(pose