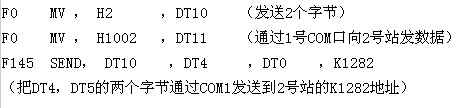

FPGA模块结构如图10所示。通过VIO控制模块,可对包事务类型、包载荷、发送地址等参数进行设置。本测试将包载荷设为256字节,读/写内存空间设为DSP的MSM(Multi-coreSharedMem

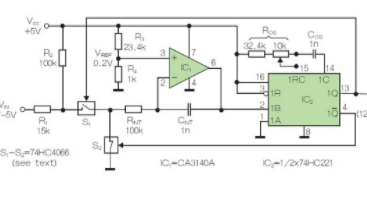

采用电压-时间转换方法改善A/D转换的线性度-在要求严格单调响应、高分辨率、较低噪声和适中速度的数据采集系统中,设计师们都喜欢使用VFC(电压-频率转换器)进行A/D转换。VFC可以产生一个频率与输入电压成正比的脉冲列。然后,微控制器或逻辑会将一个固定时间段设为门并计算该段时间内通过门的脉冲数,从而将频率转换成一个数字。