本站为您提供的使用PADS的印制板设计软件PowerPCB进行印制板设计的流程和注意事项,1本文档的目的在于说明使用PADS的印制板设计软件PowerPCB进行印制板设计的流程和一些注意事项,为一个工作组的设计人员提供设计规范,方便设计人员之间进行交流和相互检查。 2、设计流程 PCB的设计流程分为网表输入、规则设置、元器件布局、布线、检查、复查、输出六个步骤

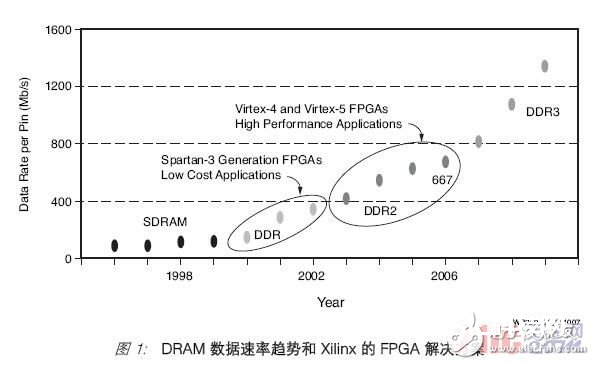

各种存储器接口控制器设计所面临的挑战和Xilinx的解决方案详解- FPGA 设计人员在满足关键时序余量的同时力争实现更高性能,在这种情况下,存储器接口的设计是一个一向构成艰难而耗时的挑战。Xilinx FPGA 提供 I/O 模块和逻辑资源,从而使接口设计变得更简单、更可靠。尽管如此,I/O 模块以及额外的逻辑还是需要由设计人员在源 RTL 代码中配置、验证、执行,并正确连接到其余的 FPGA 上,经过仔细仿真,然后在硬件中验证,以确保存储器接口系统的可靠性。

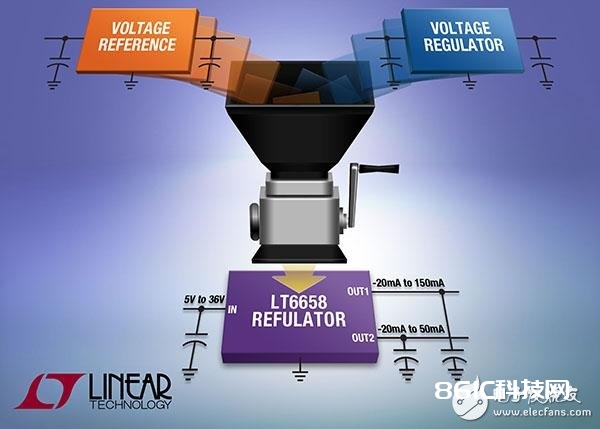

基于LT6658的200mA精密基准电压源和稳压器的设计实现-精密模拟设计人员常常依赖安静低噪声的基准电压源来为DAC和ADC转换器供电。这项任务不在基准电压源的基本职责范围内,其表面上的设计目的是为实际电源提供干净精确的稳定电压,即电源转换器的基准输入。考虑一些注意事项,基准电压源通常能够胜任为转换器基准输入提供精密电压的工作,这使得设计人员可以大胆地要求基准电压源为电流越来越高的应用供电。

一种全新的以FPGA为基础的全新锁相倍频系统方案设计-随着数字时代的到来,越来越多的领域采用集成电路来设计电路,FPGA/CPLD等EDA设计更为广大硬件工程师所接受。其模块化设计为设计人员带来了很多方便,节约了系统的开发时间,使设计人员只需要调用这些模块或者IP核,然后组合起来就可以实现一个简单的功能。全数字锁相环(DPLL)就是其中一个典型的例子。然而DPLL在应用时存在很多缺陷,例如锁相时间长、捕捉带窄等。为了避免这些缺点,本文设计了一种全新的相位跟踪倍频系统,有效地改善了DPLL的这些指标,并在项目中得到了良好的应用。

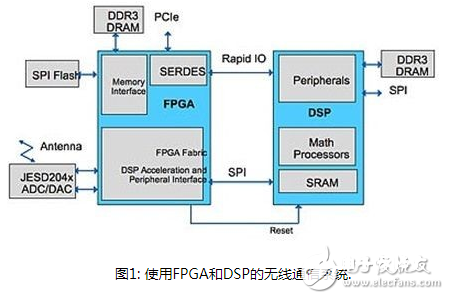

怎么利用FPGA器件保护DSP网络设计避免入侵?-对于基于数字信号处理器(DSP)的设计,如果DSP没有足够的安全能力,便特别容易受到入侵。在许多应用中,如果使用FPGA以作配合来卸载DSP的部分工作,便可以轻易实施先进的安全功能。而且,如果配合的FPGA使用flash存储技术,在芯片上存储结构中的配置位流以及关键性密匙信息,便可以实现固有的防止复制或克隆的安全性,使得设计人员能够自动保护设计避免这些类型的偷窃。

自上市以来,CMOS单电源放大器就让全球的单电源系统设计人员受益非浅。影响双电源放大器总谐波失真加噪声(THD+N)特性的主要因素是输入噪声和输出级交叉失真。单电源放大器的THD+N性能源于放大器的输

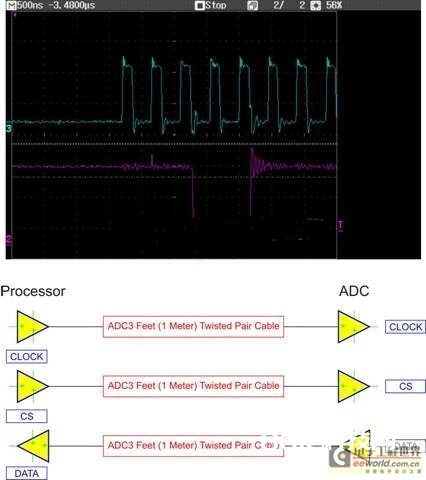

高速数字设计人员面临的一个挑战就是处理其电路板上的过冲、下冲、错配阻抗振铃、抖动分布和串扰问题。这些问题都可归入信号完整性范畴。许多高速设计人员都使用输入/输出缓冲信息规范(IBIS)建模语言来预见并