21ic讯 什么是高速印刷电路板(PCB)? 什么影响了PCB设计中的带宽? 这是我们在创建高速PCB设计时,设计人员提出的一部分常见问题与解答。由于PCB布局会极大地影响电路性能、设计时间和设计成本

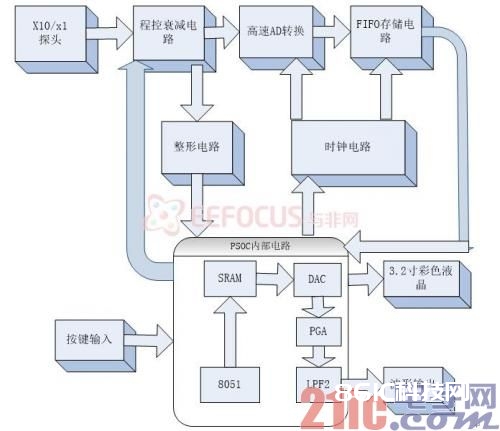

课题研究的目的和意义频谱分析仪可以方便设计人员确定干扰信号的频率范围,以便选择合理的滤波方案,但一般的频谱分析仪体积较大,不便于工业现场使用,因此设计手持式频谱分析仪,便于携带,功耗低,可长时间记录数

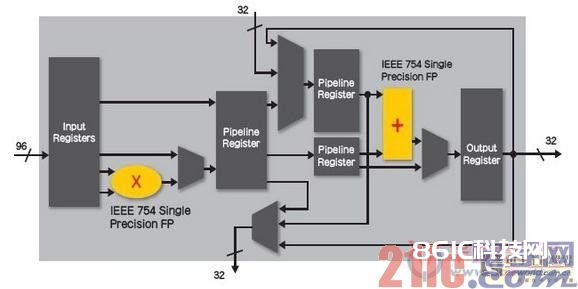

近来,Altera公司推出业界首款浮点FPGA,它集成了硬核IEEE754兼容浮点运算功能,提高了DSP性能、设计人员的效能和逻辑效率。据悉,硬核浮点DSP模块集成在Altera20nmArria10

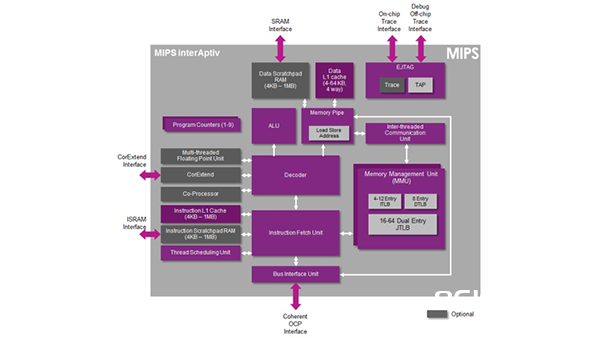

由于电子设计日渐复杂,设计人员通常需要采用各种不同类型的功能,但他们无法具备所有的专业知识、资源和时间。这促使了半导体知识产权(SIP)市场的增长,预计2017年将达到57亿美元。某些复杂设计使用的各

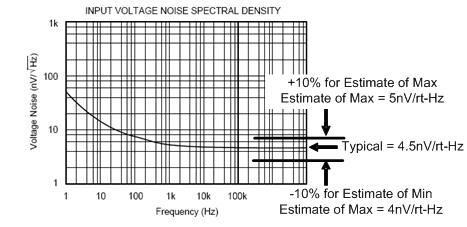

在把射频芯片或模块集成到典型的嵌入式系统中时,设计人员必须面临的一项常见任务是追踪和消除噪声和杂散信号。潜在的噪声来源包括:开关电源、来自系统其它部分的数字噪声、以及外部噪声来源。在考虑噪声时,还应考