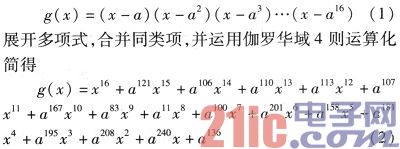

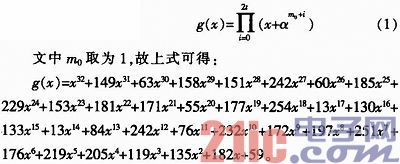

RS(Reed—Solomon)编码是一种具有较强纠错能力的多进制BCH编码,其既可纠正随机错误,又可纠正突发错误。RS编译码器广泛应用于通信和存储系统,为解决高速存储器中数据可靠性的问题

摘要:介绍了符合CCSDS标准的RS(255,223)码译码器的硬件实现结构。译码器采用8位并行时域译码算法,主要包括了修正后的无逆BM迭代译码算法,钱搜索算法和Forney算法。采用了三级流水线结构

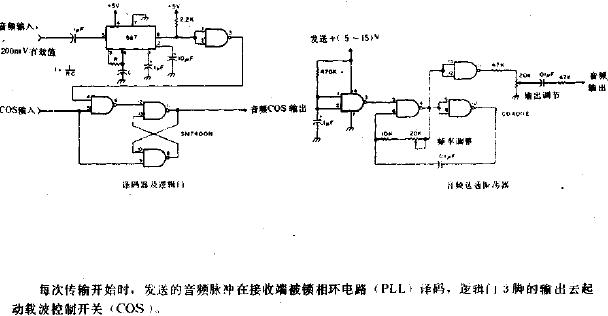

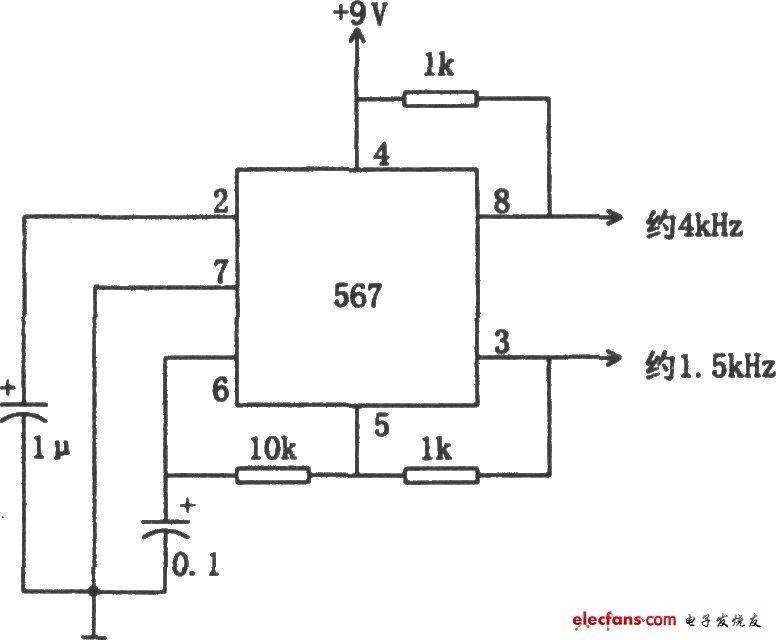

567为音频译码器,主要用于自动电话系统,识别收到的电话音调。该集成块的核心是一个高可靠性、高精度锁相环。按图示连接方式和使用的元件数值,两个输出信号频率分别为1.5kHz和4kHz。输出频率可变的方

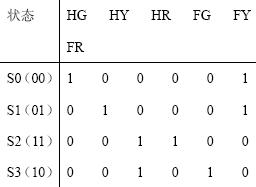

状态控制电路交通灯控制器的控制过程分为四个阶段,对应的输出有四个状态,分别用S0,S1,S2和S3表示,经过2-4译码器译码后可以控制四个电路中的其中一个工作,每个电路对应一个状态,其工作主要有三个时