RS(Reed-Solomon)编码是一种具有较强纠错能力的多进制BCH编码,其既可纠正随机错误,又可纠正突发错误。RS编译码器广泛应用于通信和存储系统,为解决高速存储器中数据可靠性的问题,文中提出了

针对319卷积编码,提出一种Viterbi译码器的FPGA实现方案。该方案兼顾了资源消耗和译码效率,通过有效的时钟和存储介质复用,实现了高速并行的译码功能,并利用Verilog语言在Xilinx IS

介绍了基于常变量可编程状态机(KCPSM)的Turbo译码器的设计。在该设计中采用Xilinx公司的嵌入式处理器IP核作为主控单元,使译码器的译码参数可根据使用情况通过程序进行调整,并在对硬件结构分析

介绍一种TPC码迭代译码器的硬件设计方案,基于软判决译码规则,采用完全并行规整的译码结构,使用VHDL硬件描述语言,实现了码率为1/2的(8,4)二维乘积码迭代译码器,并特别通过硬件测试激励来实时测量

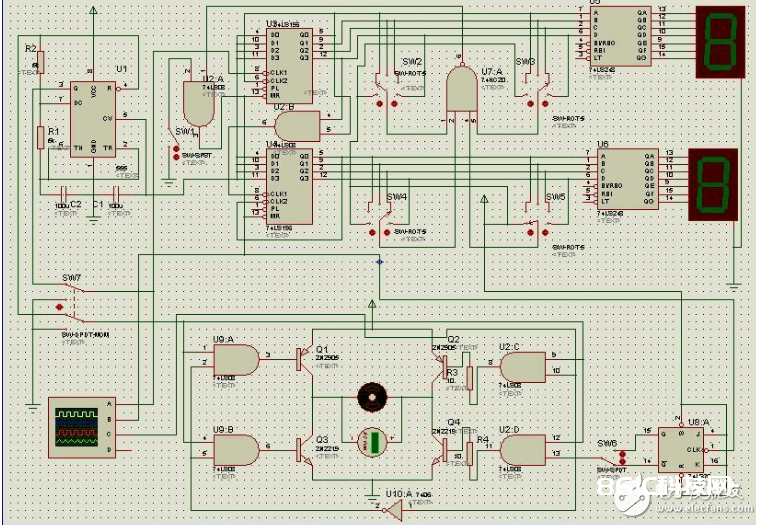

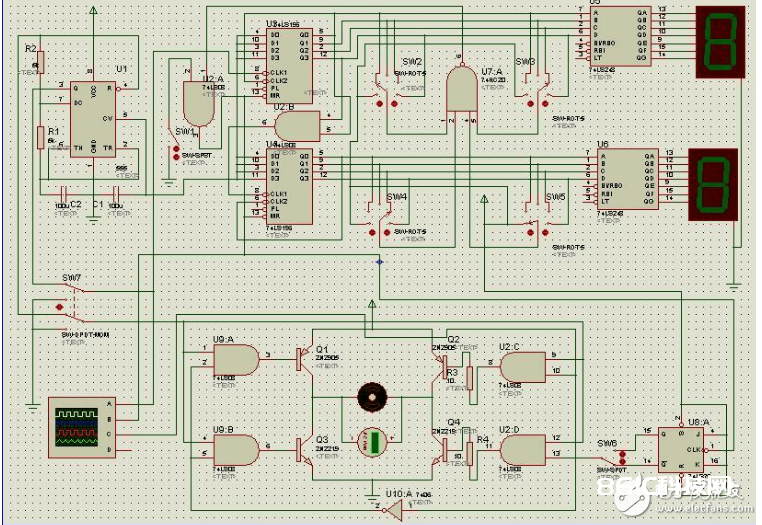

时钟脉冲计数器的输出经过3 线—8 线译码器译码其输出信号接到八位数码管的阴极Vss0、Vss1、Vss2、Vss3、Vss4、Vss5、Vss6、Vss7 端。要显示的数据信息A~H中哪一个,通过八

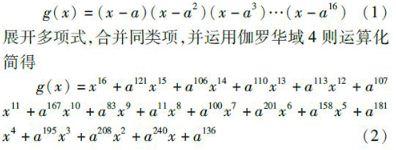

近年来,关于RS(255,223)码译码器实现的算法得到了广泛的关注,但是这些算法的实现速度都不太快,即便有速度稍高的,其占用硬件资源也较多,而一些占用硬件资源较少的算法速度却很慢。本文采用基于ME算

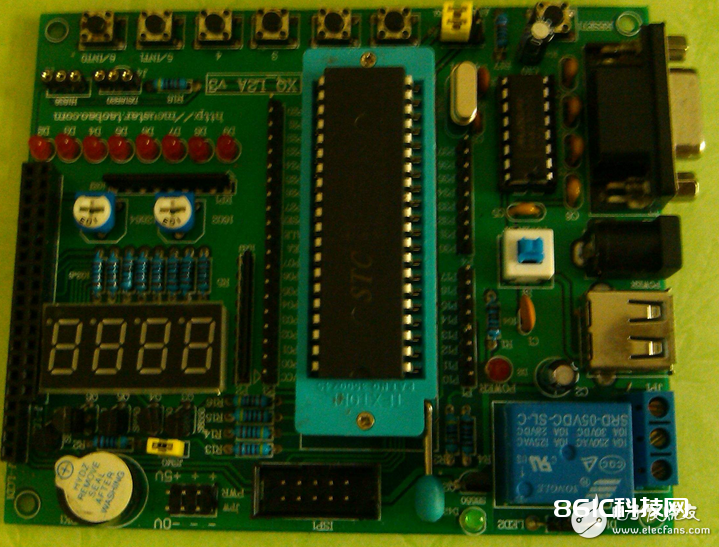

单片机如何执行代码命令,单片MCU内存如何分配?-由于本次进入指令寄存器中的内容是74H(操作码),以译码器译码后单片机就会知道该指令是要将一个数送到A累加器,而该数是在这个代码的下一个存储单元。所以