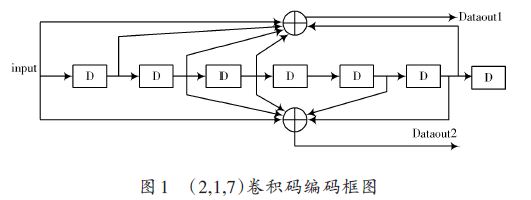

卷积码是一种重要的信道纠错编码方式,其纠错性能通常优于分组码,目前(2,1,6)卷积码已广泛应用于无线通信系统中,Viterbi译码算法能最大限度地发挥卷积码的纠错性能。阐述了802.11b中卷积码的

在通信系统中应用广泛。由于RS码的译码复杂度高,数字运算量大,常见的硬件及软件译码方案大多不能满足高速率的传输需求,一般适用于10Mbps以下。本文提出的欧氏算法和频谱结构分析相结合的RS硬件解码方案

随着NGN、3G及3G演进和NGBW等对视频、多媒体业务与网络应用的飞速发展需求,作为视频业务及存储应用核心技术的高效率 视频数字压缩编(译码)技术,愈来愈引起人们的关注,成为目前广播、视频与多媒体通