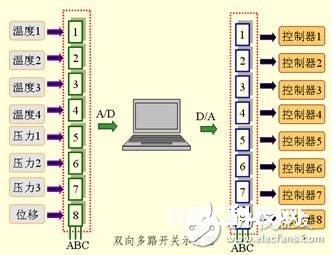

多路模拟开关结构原理-现以常用的CD4051为例,8路模拟开关的结构原理如图3-3所示。CD4051由电平转换、译码驱动及开关电路三部分组成。当禁止端INH为“1”时,前后级通道断开,即S。—S,端与Sm端不可能接通;当INH为“0”时,则通道可以被接通,通过改变控制输入端C、B、A的数值,就可选通8个通道S。~S,中的一路。

TLV320AC56/57集成电路的引脚功能和应用分析-TLV320C56/57是美国TI公司生产的音频处理集成电路(VBAP),它内含发送和接收编译码电路以及发送、接收滤波器,可用于远距离语音通讯、数字信号处理、数字音频处理、数字信号测量等系统和领域。TLV320AC56/57的主要参数如下:

通过利用FPGA器件和EP1s25F672I7芯片实现LDPC码编码器的设计-低密度奇偶校验(Low Density Parity Check Code,LDPC)码是一类具有稀疏校验矩阵的线性分组码,不仅有逼近Shannon限的良好性能,而且译码复杂度较低, 结构灵活,是近年信道编码领域的研究热点,目前已广泛应用于深空通信、光纤通信、卫星数字视频和音频广播等领域。LDPC码已成为第四代通信系统(4G)强有力的竞争者,而基于LDPC码的编码方案已经被下一代卫星数字视频广播标准DVB-S2采纳。

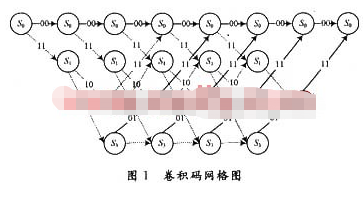

采用可编程逻辑器件的译码器优化实现方案-由于卷积码优良的性能,被广泛应用于深空通信、卫星通信和2G、3G移动通信中。卷积码有三种译码方法:门限译码、概率译码和Viterbi算法,其中Viterbi算法是一种基于网格图的最大似然译码算法,是卷积码的最佳译码方式,具有效率高、速度快等优点。从工程应用角度看,对Viterbi译码器的性能评价指标主要有译码速度、处理时延和资源占用等。本文通过对Viterbi译码算法及卷积码编码网格图特点的分析,提出一种在FPGA设计中,采用全并行结构、判决信息比特与路径信息向量同步存储以及路径度量最小量化的译码器优化实现方案。测试和试验结果表明,该方案与传统的译码算法相比,具有更高的速度、更低的时延和更简单的结构。

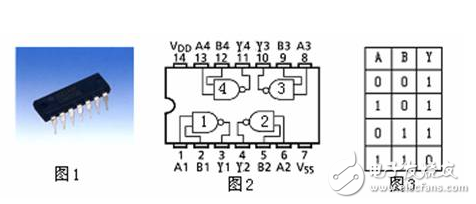

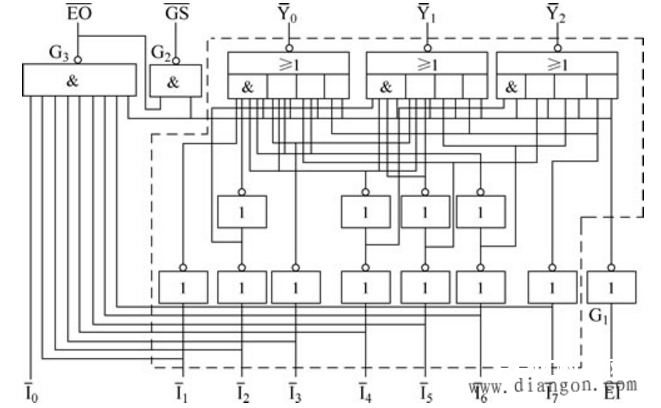

本站为您提供的74ls148可以用什么代替,本文主要介绍了74ls148可以用什么芯片代替?74LS148是8线-3线优先编码器,共有54/74148和54/74LS148两种线路结构型式,将8条数据线(0-7)进行3线(4-2-1)二进制(八进制)优先编码,即对最高位数据线进行译码。利用选通端(EI)和输出选通端(EO)可进行八进制扩展。