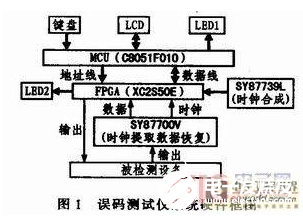

以FPGA为核心的高速误码测试仪设计流程概述-误码分析仪作为数字通信系统验收、维护和故障查询的理想工具,广泛应用于同轴电缆、光纤、卫星及局间中继等符合CEPT(European Confence of Postal and Telecommunications Administrations)数字系列通信系统传输质量的监测。评价一个通信系统的可靠性的指标就是检测该通信系统在数据传输过程中误码率的大小,本文设计的高速信号误码测试仪,用于对EPON中接收和发送突发光信号的接收模块的可靠性进行检测。目前误码分析仪的工作模式已发展到如下4种:分析仪模式、发生器模式、分析仪/发生器模式、直通模式。本设计中的误码测试仪属于第3种类型,即该误码测试仪可以产生测试的码流,又可以进行误码测试。