MSP430单片机实现模拟串口通信的设计-1、背景:

很多时候由于硬件资源有限,但又需要使用串口通信,此时可以考虑使用模拟串口;

2、前提:

要实现特定bps的串口速率,需要相应频率的定时器,保证误码率在可以接受的范围内;

例如:

1MHz的时钟最高可模拟9600bps的通信速率:1M/9600 = 104 误码率1%

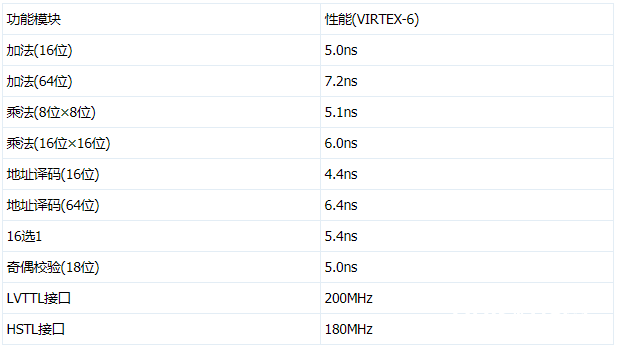

基于XCV200/300PQFP240和TMS320C40实现背板开发设计-在移动通信和高速无线数据通信中,多径效应和信道带宽的有限性以及信道特性的不完善性导致数据传输时不可避免的产生码间干扰,成为影响通信质量的主要因素,而信道的均衡技术可以消除码间干扰和噪声,并减少误码率。其中判决反馈均衡器(DFE)是一种非常有效且应用广泛得对付多径干扰得措施。目前DFE大致有以下几种实现方法:

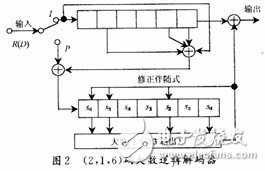

采用VHDL语言实现卷积码编解码器设计-数字信息在有噪信道中传输时,会受到噪声干扰的影响,误码总是不可避免的。为了在已知信噪比的情况下达到一定的误码率指标,在合理设计基带信号,选择调制、解调方式,并采用频域均衡或时域均衡措施的基础上,还应采用差错控制编码等信道编码技术,使误码率进一步降低。

基于Cyclone系列FPGA器件和UART功能实现误码率测试仪器的设计-在通信系统的设计实现过程中,都需要测试系统的误码性能。而常见的误码率测试仪多数专用于测试各种标准高速信道,不便于测试实际应用中大量的专用信道,并且价格昂贵,搭建测试平台复杂。随着大规模集成电路的迅速发展,FPGA在保持其集成度高,体积小,功耗低,性价比高特性的同时,能够实现越来越复杂设计功能,日益广泛的应用于通信设备的设计实现。

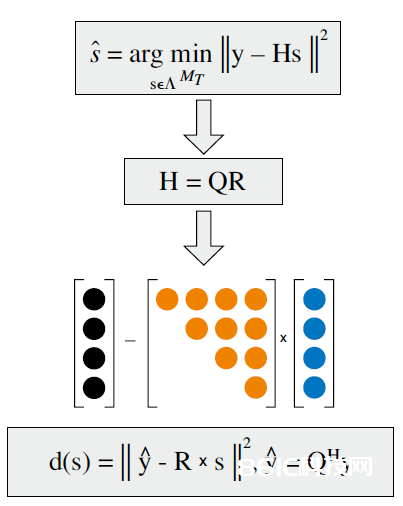

MIMO无线系统最佳硬判决检测方式是最大似然检测器。ML检测因为比特误码率 (BER)性能出众,非常受欢迎。不过,直接实施的复杂性会随着天线和调制方案的增加呈指数级增强,使ASIC或FPGA仅能用于使

差错控制编码技术对改善误码率、提高通信的可靠性具重要作用。RS码既可以纠正随机错误,又可以纠正突发错误,具有很强的纠错能力,在通信系统中应用广泛。由于RS码的译码复杂度高,数字运算量大,常见的硬件及软

差错控制编码技术对改善误码率、提高通信的可靠性具重要作用。RS码既可以纠正随机错误,又可以纠正突发错误,具有很强的纠错能力,在通信系统中应用广泛。由于RS码的译码复杂度高,数字运算量大,常见的硬件及软

差错控制编码技术对改善误码率、提高通信的可靠性具重要作用。RS码既可以纠正随机错误,又可以纠正突发错误,具有很强的纠错能力,在通信系统中应用广泛。由于RS码的译码复杂度高,数字运算量大,常见的硬件及软