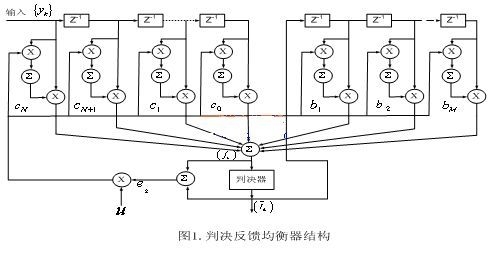

在移动通信和高速无线数据通信中,多径效应和信道带宽的有限性以及信道特性的不完善性导致数据传输时不可避免的产生码间干扰,成为影响通信质量的主要因素,而信道的均衡技术可以消除码间干扰和噪声,并减少误码率。

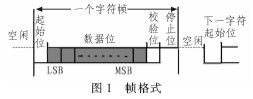

为了实现PC机与CPLD的通信,进行了相应的研究。分析了RS-232C通信协议,自定义了数据包传输格式。根据UART模块工作状态多的特点,应用了有限状态机理论进行编程实现。为降低误码率,应用16倍频技

语音编码使每个语音参数所承载的信息量加大,对信道误码很敏感。在条件较为苛刻或者恶劣的高误码率窄带无线信道环境下,例如:野外无线信道、短波或超短波信道、保密通信等,信道误码对重建语音质量影响很大。而无线

10G以太网系统中的并行CRC编解码器的设计-通信系统不可避免地要受到各种干扰的影响,使接收端收到的信息与发送端发出的信息不一致,即接收端收到的信息产生了误码。为了降低数据通信线路传输的误码率,通常有

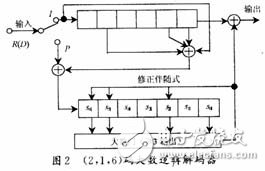

采用VHDL语言实现卷积码编解码器设计-数字信息在有噪信道中传输时,会受到噪声干扰的影响,误码总是不可避免的。为了在已知信噪比的情况下达到一定的误码率指标,在合理设计基带信号,选择调制、解调方式,并采用频域均衡或时域均衡措施的基础上,还应采用差错控制编码等信道编码技术,使误码率进一步降低。

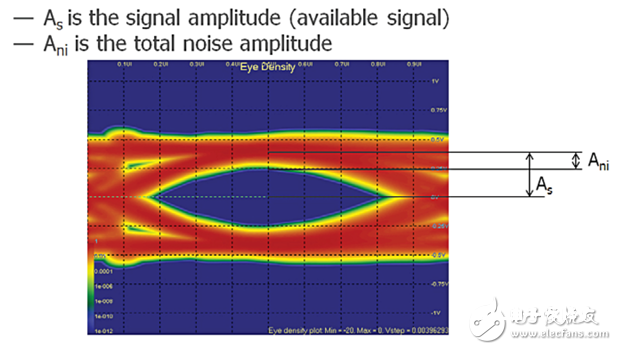

本站为您提供的Channel Operating Margin:与误码率进行比较, 一年多前,IEEE 发布了针对千兆以太网的 802.11bj 规范。此外,该规范还定义了 Channel Operating Margin (COM) 通道的一种质量评估方式。