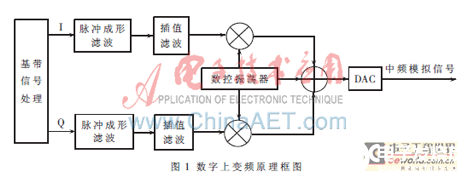

基于FPGA的高效灵活数字上变频实现设计-软件无线电的基本思想是把A/D变换器尽可能地靠近射频天线,用软件实现无线电系统的各种功能[1]。数字上变频器是软件无线电中发射机的核心部分,它的基本功能是增加基带信号采样率并将其上变频到载波频率上,经过发射天线发射出去。采用专用芯片实现数字上变频器集成度高,应用方便,但是缺少灵活性,在软件无线电中的应用受到限制,因此研究使用可编程的FPGA实现数字上变具有重要意义。

SoPC与CORDIC算法相结合的通用调制解调器设计方案-软件无线电要求在通用硬件平台上通过运行不同软件实现多种调制解调方式,这就要求为信号的调制及解调建立通用模型。当代无线通信中,理论上各种通信信号都可采用正交调制方法加以实现,所以,采用正交调制可以建立统一的模型,适用于软件无线电实现。

一种基于FPGA的神经网络硬件实现方案详解-人工神经网络在智能控制、模式识别、图像处理等领域中应用广泛。在进行神经网络的应用研究时,人们可以将神经网络模型或算法在通用的计算机上软件编程实现,但很多时间浪费在分析指令、读出写入数据等,其实现效率并不高。软件实现的缺点是并行程度较低,因此利用软件实现神经网络的方法无法满足某些对数据实时处理要求较高的场合(如工业控制等领域)。

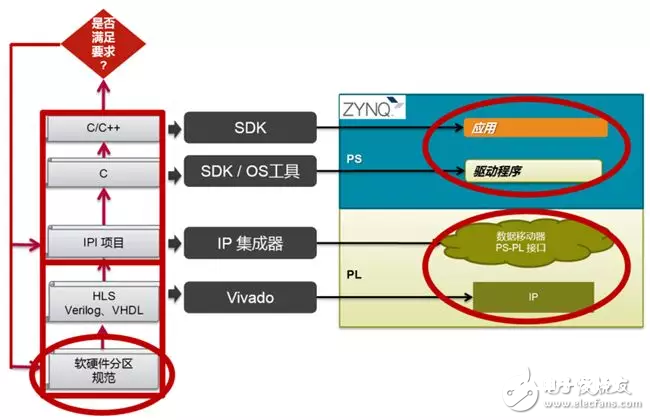

Zynq开发流程的捷径SDSoC-让我们先来看看一个典型的Zynq SoC开发流程(如图1):开发者首先需要对软硬件进行分区,即确定系统哪些部分放入PL(可编程逻辑)中进行硬件加速,哪些部分在PS(处理器系统)中用软件实现;接下来,要完成软/硬件之间的连接,包括使用怎样的DataMover、PS与PL之间的接口如何配置等;之后要完成配套的软件驱动和应用程序的开发。

什么是单片机烧写软件?如何烧写-什么是单片机烧写软件? 什么是单片机烧写软件? 简单点说,就是把你写好代码(C或者是汇编)专程的机器语言通过一定的方式下载到单片机中。称为烧写。 烧写软件很多,方式也很多,主要看你的单片机型号.

针对RISC-V设计提供全面软件工具链和IP内核的FPGA- 美高森美公司(Microsemi Corporation)宣布成为首家针对RISC-V设计提供全面软件工具链和知识产权(IP)内核的可编程逻辑器件(FPGA)供应商。其RV32IM RISC-V内核适用于美高森美 IGLOO2 FPGA、 SmartFusion2系统级芯片(SoC) FPGA或RTG4 FPGA,具备运行于Linux平台并基于Eclipse的SoftConsole集成开发环境(IDE)和Libero SoC设计套件,提供全面的设计支持。