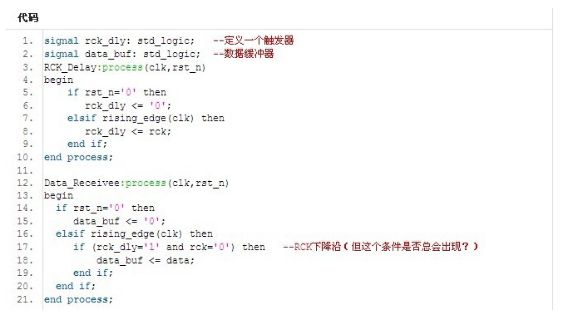

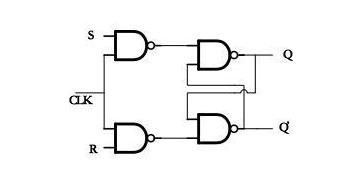

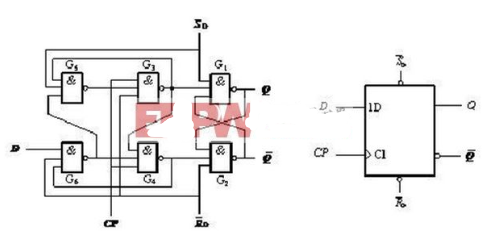

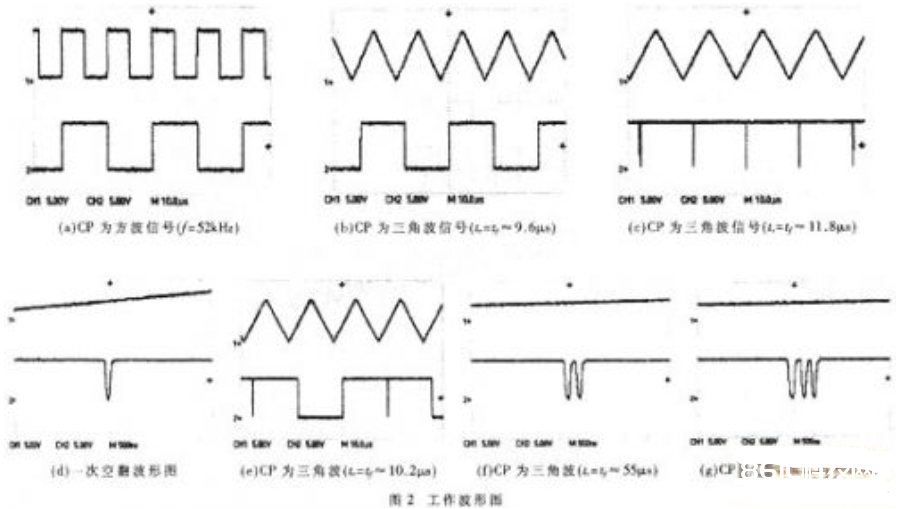

D触发器基本原理-负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。边沿D触发器也称为维持-阻塞边沿D触发器。

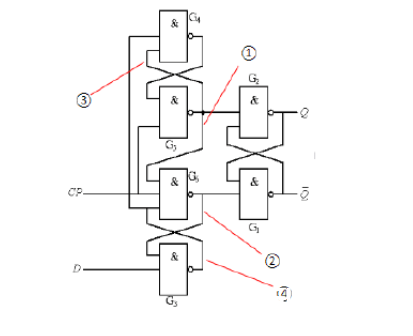

CMOS传输门的边沿触发器电路结构及工作原理-当CP′=0,CP′=1时,TG1导通,TG2截止,D端输入信号送人主触发器中,使Q′=D,Q′=D,但这时主触发器尚未形成反馈连接,不能自行保持。Q′、Q′跟随D端的状态变化;同时,由于TG3截止,TG4导通,所以从触发器形成反馈连接,维持原状态不变,而且它与主触发器的联系被TG3切断。