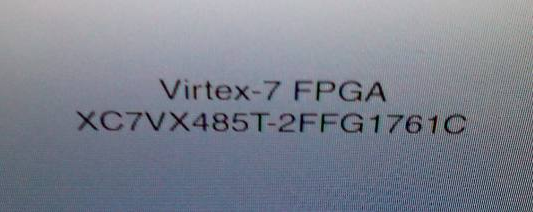

关于FPGA芯片命名规则的解释-同一款芯片可以有多个速度等级,不同的速度等级代表着不同的性能,不同的性能又导致芯片价格的巨大差异。芯片的速度等级不是设计出来的,而是在芯片生产出来之后,实际测试标定出来的。

设计FPGA系统的三个基本原则是什么,了解一下-在这种方法中面积的复制可以换取速度的提高。支持的速度越高,就意味着可以实现更高的产品性能。一些注重产品性能的应用领域可以采用并行处理技术,实现面积换速度。

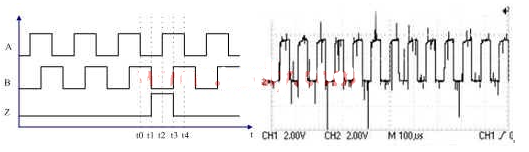

采用FPGA器件实现滤波器的设计和验证方法-光电脉冲编码器是一种集光、机、电为一体的用于检测机械位移或间接检测速度的光电传感器,根据其用于检测角位移及旋转速度或直线位移及直线运动速度又分为光电轴角编码器和直线编码器。根据形成代码的方式不同,光电轴角编码器分为增量式和绝对式两大类。光电脉冲编码器因其精度高、响应快、使用可靠等优点,已广泛应用于数控机床、轧钢、纺织器械、电梯、印刷、卷烟机、机器人、磁卡机、电脑刺绣机等工业控制和测试领域。

采用DSP实现H.324可视电话系统设计-以PC机为平台,利用现有的声卡、视频要集卡和调制解调器作为输入和输出设备,采和基于WINDOWS的多线程技术软件实现H.263视频器、解码/发送、接收、显示等多个任务。在实际应用系统时需要考虑到PC的处理能力、与接收端的连接和相应的图像格式等问题,可以在编码模块中采用汇编语言,提高执行速度,并引入MMX技术,进一步提高执行速度。它的特点是成本低、配置少,便于移植和升级,但对计算机的处理能力、编解码的算法速率的要求比较高,一般难于达到实时要求。

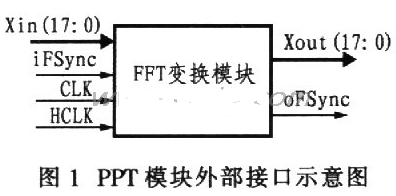

基于FPGA器件实现微波接力机中的FFT模块设计-对实现FFT的工程,目前通用的方法是采用DSP、FFT处理电路及FPGA。用DSP实现FFT的处理速度较慢,不能满足某些高速信号实时处理的要求;专用的FFT处理器件虽然速度较快,但是价格相对昂贵且外围电路相对复杂;采用新一代的FP-GA来实现FFT兼有二者的优点。FPGA资源丰富、易于借助并行流水的特点来实现FFT,不但性能稳定、经济性好,而且可以大大缩短计算的耗时。以Altera公司的Stratix系列FPGA为例,它具有多达79 040个逻辑单元、7 MB的嵌入式存储器、优化的数字信号处理器和高性能的I/O能力,非常方便以全并行流水方式进行FFT处理。

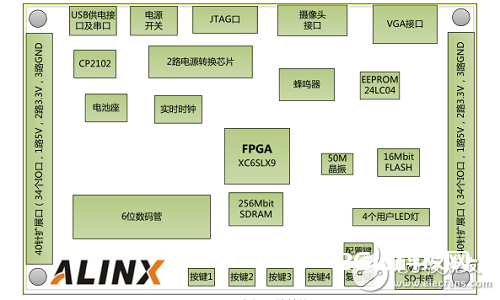

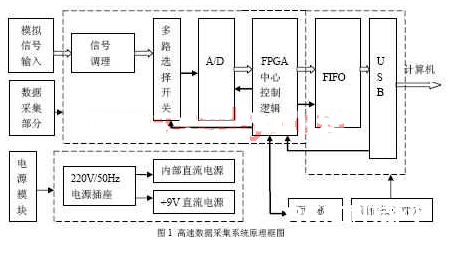

基于FPGA +AD7609的数据采集系统的实现和设计-随着信息技术的发展,特别是各种数字处理器处理速度的提高,人们对数据采集系统的要求越来越高,特别是在一些需要在极短时间内完成大量数据采集的场合,对数据采集系统的速度提出了非常高的要求。

关于反熔丝FPGA的结构和原理以及其在密码芯片设计中的运用浅析-随着计算机和通信的发展,信息传输过程中信息安全的重要性越来越受到人们的重视。在信息传输过程中,人们普遍采用将待传输的信息加密进行传输,然后在收端进行解密还原信息。对信息的加解密通常采用两种方法:软件加解密和硬件加解密。软件加解密实现简单,但须对密码算法进行多重保护存放且加解密速度较慢,而硬件加解密可加快加解密运行速度。在当今信息网络化的环境下,对加密的速度要求将越来越高,如:在ATM、帧中继、ISDN PRI等领域的加密,将会有数兆或数十兆以上的速度要求,所以硬件加密将是今后首选的加密手段。目前运用的硬件加解密,大都采用SRAM型的FPGA实现,必须外挂一EEPROM存储加载FPGA的数据,这就为信息安全带来了巨大隐患,特别是在运用于军事、政府等部门的保密通信产品中。要求重要信息不得以明文的形式出现

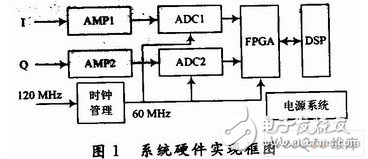

为了发挥FPGA硬件实现的速度优势 算法进行优化是必须要做的-“No PP,No WAY”这是个眼见为实的世界,这是个视觉构成的信息洪流的世界。大脑处理视觉内容的速度比文字内容快6万倍,而随着智能手机的普及,图片、视频的产生和分享已经是人们在社交平台上的基本交流方式。用户通过手机、平板、电脑上传和分享自己的图片,而且这个趋势是每年都在增长(参见图1)。

基于Altera的FPGA器件和VHDL语言实现数据采集系统的设计-传统的数据采集系统,通常采用单片机或DSP作为主要控制模块,控制ADC、存储器和其他外围电路的工作。随着数据采集对速度性能的要求越来越高,传统采集系统的弊端就越来越明显。单片机的时钟频率较低且需用软件实现数据采集,这使得采集速度和效率降低,此外软件运行时间在整个采样时间中也占很大的比例。