如何调整STM32单片机中flash与时钟速率之间的关系-void Flash_Init(void)

{

// 调整flash与时钟速率之间的关系

FLASH-》ACR |= FLASH_ACR_LATENCY;

}

void Flash_Unlock(void)

{

// FLASH-》CR 的第7位为解锁的标志位或者上锁的操作位

while(FLASH-》CR & FLASH_CR_LOCK)

{

FLASH-》KEYR = FLASH_FKEY1;

FLASH-》KEYR = FLASH_FKEY2;

}

}

void Flash_Lock(void)

{

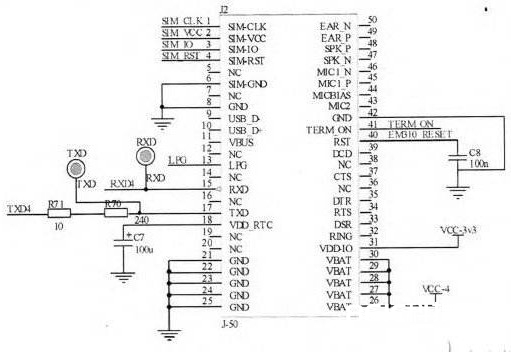

MSP430单片机实现模拟串口通信的设计-1、背景:

很多时候由于硬件资源有限,但又需要使用串口通信,此时可以考虑使用模拟串口;

2、前提:

要实现特定bps的串口速率,需要相应频率的定时器,保证误码率在可以接受的范围内;

例如:

1MHz的时钟最高可模拟9600bps的通信速率:1M/9600 = 104 误码率1%

浅析六种常用的单片机通信协议-在单片机的应用中,通信协议是必不可少的一部分,上位机与下位机,单片机与单片机,单片机与外设模块之间的通信都需要通信协议实现信息交换和资源共享。由于设备之间不同的传输速率、电气特性、可靠性要求的不同,产生了许多类型的适用于不同情况的通信协议,并被广泛接受和使用。

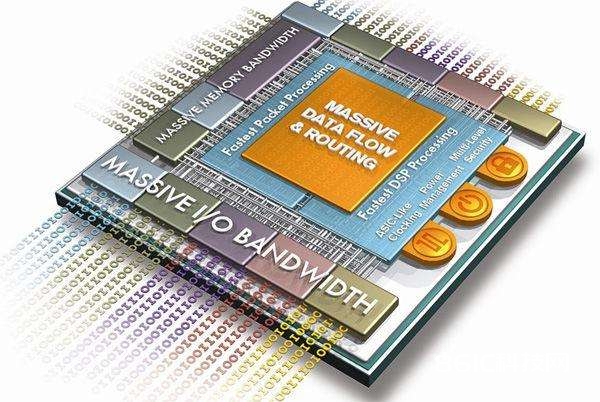

基于FPGA芯片实现单片式8路高速数字信号分析仪的设计-由于数字信号只有高电平和低电平两种情况,因此,用单片机 (MCU)就可直接实现多路数字信号进行采集和逻辑分析。但由于单片机的时钟频率较低,完成一次采样的时间受程序执行指令速度的限制,采样速率通常不超过1MHz。因此,用单片机只能实现对低速率数字信号进行逻辑分析。

关于Virtex和Kintex UltraScale架构的FPGA和Vivado开发工具的机构要点- 基于UltraScale架构的FPGA实现数据传输机制是通过将高性能的并行专用IO接口和高速的串行收发器结合起来实现的,UltraScale架构的串行收发器传送数据的速率能够达到16.3Gbps,满足主流的串行协议要求,当然传输速率也能够达到32.75Gbps,允许25G+比特位的地板设计,而且相对以前的收发器而言,能够大大降低每比特位传输的功耗。UltraScale架构的FPGA芯片中的收发器都兼容PCIe3.0和PCIe4.0,专用的PCIe集成模块支持PCIe3.0 X8型端口和根端口的设计需求。

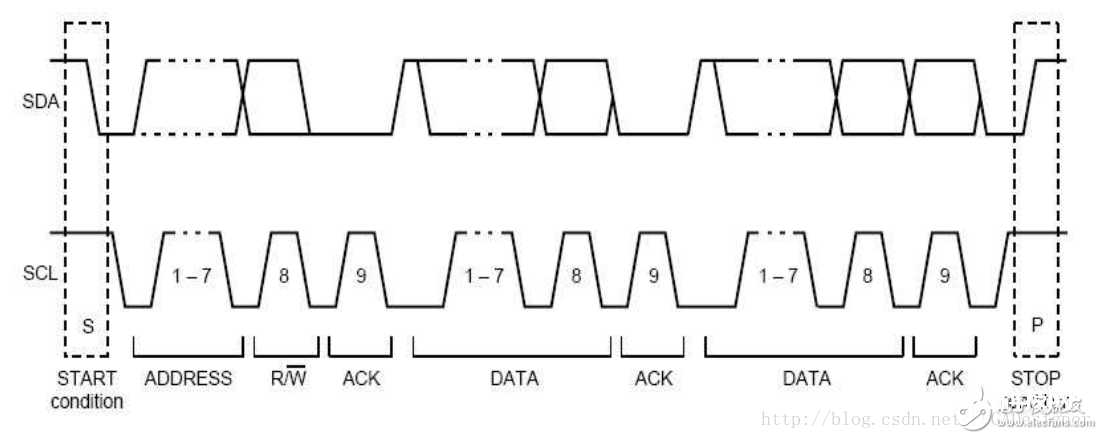

FPGA基础知识之IIC协议读写解析-很多数字传感器、数字控制的芯片(DDS、串行ADC、串行DAC)都是通过IIC总线来和控制器通信的。不过IIC协议仍然是一种慢速的通信方式,标准IIC速率为100kbit/s,快速模式速率为400kbit/s。本文致力于讲述如何用计数器控制和分频时钟控制两种方式完成IIC的读写操作。 IIC协议 IIC协议是一种多机通讯,由SDA数据线和SCL时钟线构成串行总线,所有的IIC设备都可以挂载到总线上,但每个设备都有唯一的设备读地址和设备写地址。在使用IIC作为数字接口的芯片

莱迪思推出支持速率高达10 Gbps嵌入式MIPI D-PHY接口的FPGA-莱迪思半导体公司(NASDAQ:LSCC),低功耗可编程器件的领先供应商,今日宣布拓展其屡获殊荣的Crosslink™-NX系列产品,推出专门用于高级驾驶辅助系统(ADAS)和车载娱乐信息系统等汽车应用的全新FPGA。

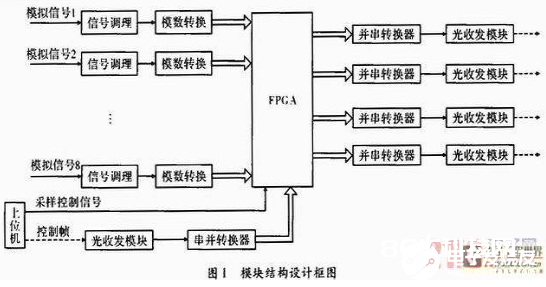

以FPGA为核心的高速数据采集控制模块设计流程概述-在雷达、通信、气象、军事监控及环境监测等领域,现场信号具有重要的作用。这些信号的主要特点是:实时性强、数据速率高、数据量大、处理复杂。为能够完整、准确地捕获到各种信号并及时进行处理,需要临测系统能够具备任意长度连续采集和存储的功能,且具有较高的数据传输率。考虑到FPGA拥有丰富的可编程I/O引脚、时钟频率高、时序控制精确、运行速度快、编程配置灵活等特点,采用其作为核心控制模块。因为光纤通信使用简单的点到点互连,具有传输损耗低、传输频带宽、速率高和抗电磁干扰等优点,在增加可靠性的同时降低了电缆连接的复杂程度,所以采用光纤作为信号传输媒介。

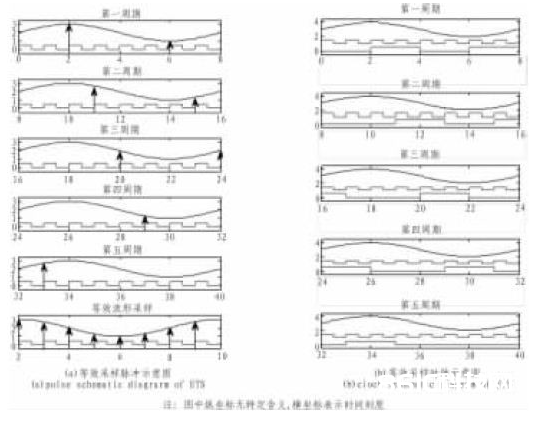

基于FPGA采样技术的等效时间采样原理剖析-在现代电子测量、通讯系统以及生物医学等领域,经常涉及对宽带模拟信号进行数据采集和存储,以便计算机进一步进行数据处理。为了对高速模拟信号进行不失真采集,根据奈奎斯特定理, 采样频率必须为信号频率的2 倍以上,但在电阻抗多频及参数成像技术中正交序列数字解调法的抗噪性能对信号每周期的采样点数决定,采样点数越多,抗噪性能越高。当采样信号频率很高时,为了在被采样信号的一周期内多采样,就需要提高采样时钟的频率,但是由于系统的ADC 器件时钟速率并不能达到要求的高频速率或者存储处理速度等不能满足要求因此我们可以采用低速ADC 器件通过等效时间采样来对宽带模拟信号进行数据采集从而使系统易于实现。