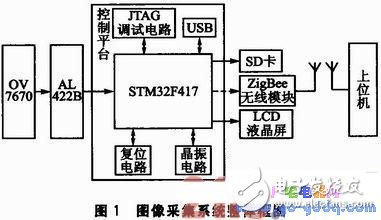

基于STM32F417的图像采集系统设计实现-本文所设计的基于STM32F417的图像采集系统具有采集图像质量无损、实时性好、功耗低、成本低等优势,适合在对信息采集的实时性和图像质量方面有较高要求的系统中应用。

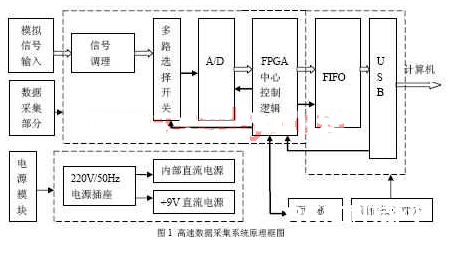

一个基于FPGA和USB 2.0的高速CCD声光信号采集系统设计-在现代通信和雷达领域中,宽带、高增益、实时并行处理是现代接收机的重要标志。因而,这种具有高速并行处理能力和特有的大带宽性能的声光处理系统具有巨大的潜在优势。以声光器件为基础的接收机除了具有宽带、高增益、实时并行处理等特点外,还具有容量大,体积小,功耗低等优点。因而,采用声光信号处理技术解决带宽、高增益和实时并行处理问题具有重要意义,声光信号的采集系统的设计是整个声光系统关键之一。这里设计了一个基于FPGA和USB 2.0的高速CCD声光信号采集系统,为声光信号采集提供了硬件平台。

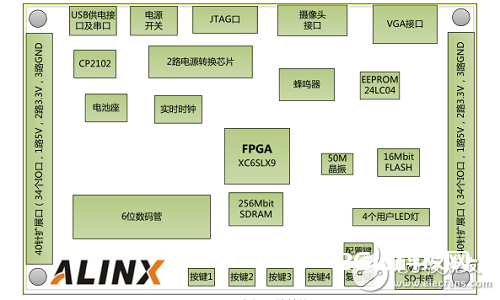

基于EP1K10TC100-3 FPGA和微控制器实现数据采集系统的应用方案-基于 FPGA 的数据采集系统的总体功能模块如下图1 所示。系统有由FPGA、串行被动 配置模块、USB 通信模块、电源模块、显示模块、模数转换模块、数模转换模块等几个模 块组成。

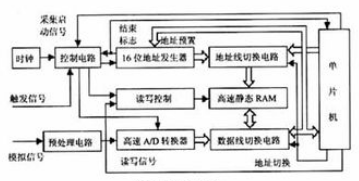

基于复杂可编程逻辑器件实现数据采集系统的软硬件设计-以往的数据采集系统多数采用单片机、DSP等微处理器产生A/D转换芯片所需要的控制时序,以及通道转换所需要的时序逻辑信号,这样会占用CPU较多的时间。本文介绍基于CPLD的高速高精度数据采集系统设计方法,所需控制时序及地址译码等电路均由CPLD产生,并将转换结果放于双端口RAM中,CPU随时从双端口RAM中读取转换结果,大大提高系统的数据采集速度。

基于FPGA +AD7609的数据采集系统的实现和设计-随着信息技术的发展,特别是各种数字处理器处理速度的提高,人们对数据采集系统的要求越来越高,特别是在一些需要在极短时间内完成大量数据采集的场合,对数据采集系统的速度提出了非常高的要求。

采用FPGA器件控制ADC和数据传输实现数据采集系统的设计-数据采集系统是计算机测控系统中不可或缺的组成部分,是影响测控系统的精度等性能指标的关键因素之一。常用数据采集方案是以微处理器为核心控制多个通道的信号采集、预处理、存储和传输,即用软件实现数据的采集,这在一定程度上局限了数据采集的速度、效率及时序的精确控制。

基于Altera的FPGA器件和VHDL语言实现数据采集系统的设计-传统的数据采集系统,通常采用单片机或DSP作为主要控制模块,控制ADC、存储器和其他外围电路的工作。随着数据采集对速度性能的要求越来越高,传统采集系统的弊端就越来越明显。单片机的时钟频率较低且需用软件实现数据采集,这使得采集速度和效率降低,此外软件运行时间在整个采样时间中也占很大的比例。

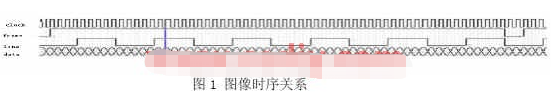

采用可编程逻辑器件实现图像目标发生器的应用方案-在CCD图像采集中,需要对图像采集系统的性能进行评估,而由于CCD相机的研制时间长,研制成本高,并且不易于控制,因此,研制出开发周期短、易于控制的图像目标发生器成为评估图像采集系统中很重要的一步。