基于通过寄存器和调用库函数的方式,对比测试STM32读写IO时间-通过在线调试的方式,可以看出1条C语句:GPIOA -> BSRR = 1<<3;//PA3输出高电平 对应3条汇编指令:MOVS r0,#0x08 ;把立即数0x08传送给寄存器r0 LDRr1,[PC,#8] ;从地址(PC+8)处读取一个字到寄存器r1 STRr0,[r1,#0x00] ;把r0中的低字节存储到地址(r1+0)处 由于Cortex-M3的大部分汇编指令均为单周期指令,理论上PA3输出高电平为3个时钟周期, 即3*(1/72)us = 42ns,经示波器实测输出高电平时间约为:42ns左右。

基于PIC单片机对SC1621摇控器的控制-;*APPLICATION NOTE E6000 ICEXPLORER ******************

;* Title: ;

;SC6121的遥控器发射码依次为:同步头(引导码)+32位数据码 ;

;(用户码低8位+用户码高8位+键码+键码的反码) ;

;引导码是由9MS的高电平加4.5MS的低电平构成, ;

;我们接收到的刚好反相为9MS的低电平加4.5MS的高电平。 ;

怎样用STM32单片机的GPIO控制LED显示状态-ODR寄存器可读可写:既能控制管脚为高电平,也能控制管脚为低电平。

管脚对于位写1 gpio 管脚为高电平,写 0 为低电平

BSRR 只写寄存器:[color=Red]既能控制管脚为高电平,也能控制管脚为低电平。

对寄存器高 16bit 写1 对应管脚为低电平,对寄存器低16bit写1对应管脚为高电平。写 0 ,无动作

BRR 只写寄存器:只能改变管脚状态为低电平,对寄存器 管脚对于位写 1 相应管脚会为低电平。写 0 无动作。

51单片机PPM波的测试设计-先说说PPM波,从图上可以看出周期为20ms,冠丽控实际是6通控,但预留两通没有使用。通道的高电平区间为0.765~1.6ms 低电平时间为0.395ms引导波形的高电平 时间为10.165ms。

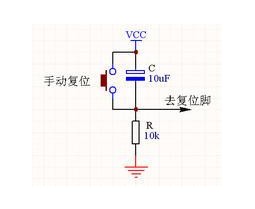

51单片机的复位方式及原理-51单片机采用高电平复位。以当前使用较多的AT89系列单片机来说,电路图如下。在复位脚加高电平2个机器周期可使单片机复位。复位后的主要特征是各IO口呈现高电平,程序计数器从零开始执行程序。

AVR单片机键盘程序设计-uchar key_temp;

PORTC|=0x07; //向PORTC.0–PORTC.2写入高电平

DDRC=0x00; //把PORTA设置为输入模式

key_temp=PINC&0x07; //读取PORTA.0–PORTA.2上的值并屏蔽其它位

/*****如果K0—K6按下,key_temp就为相应的键值,如果K7–K15按下,则读入PINC.0–PINC.2都为高电平,key_temp==7

然后PORTC.0–PORTC.2依次输出低电平,判断K7–K15那个键按下**********/

if(key_temp==7) //判断K7–K9是否按下

51单片机的模拟开关设计-单片机对开关状态的检测相对于单片机来说,是从单片机的P3.0端口输入信号,而输入的信号只有高电平和低电平两种,当拨开开关K1拨上去,即输入高电平,相当开关断开,当拨动开关K1拨下去,即输入低电平,相当开关闭合。单片机可以采用JB BIT,REL或者是JNB BIT,REL指令来完成对开关状态的检测即可。

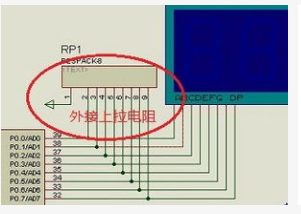

如何为51单片机的P0口选择合适的上拉电阻-P0口作为I/O口输出的时候时,输出低电平为0输出高电平为高组态(并非5V,相当于悬空状态,也就是说P0 口不能真正的输出高电平)。给所接的负载提供电流,因此必须接上拉电阻(一电阻连接到VCC),由电源通过这个上拉电阻给负载提供电流。

51单片机解码PPM波的设计-先说说PPM波,从图中可以看出周期为20ms,冠丽控实际是6通控,但预留两通没有使用。通道的高电平区间为0.765~1.6ms 低电平时间为0.395ms引导波形的高电平 时间为10.165ms。