跟着示波器用户对速度更快、功耗更低和体积更小的存储器的需求日积月累,双倍数据速率(DDR)存储器技能在曩昔五年里得到了巨大的开展。

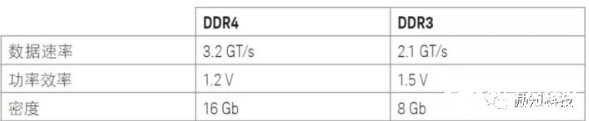

DDR4 的意义是具有双倍数据速率的第四代 SDRAM 存储器。与 DDR3 比较,DDR4 的数据传输带宽大幅添加,并且在速度、密度和功率等方面都逾越以往。这些技能进步推进企业级运用、微型服务器运用和平板电脑运用的功用和能效进一步进步,让规划人员能够规划芯片更小、功耗更低、散热更少的器材。

DDR4 存储器的体系结构整合了 DDR3(双向 DQS)和相似 GDDR5 的数据总线(CRC 和数据误码检测功用)两方面的要害特性。但 DDR4 信号也有一些特性与上一代 DDR 处理方案天壤之别。这些要害差异促进新的测验办法面世。

信号完整性的问题

信号完整性关于存储器体系的牢靠运转至关重要。测验信号完整性,首要应从物理层开端,数据在这一层经过时钟上升沿和下降沿进行传输。但是在测验 DDR4 存储器的物理层时遇到了一些新的应战。

依照电子器材工程联合会(JEDEC)标准的要求,在施行电子、时序和眼图测验时都需求履行输入和输出丈量,其间包含很多测验操作以保证存储器体系正常运转,不会发生过错。DDR4 的速度进步还要求经过别离读写周期来丈量 AC 时序参数。

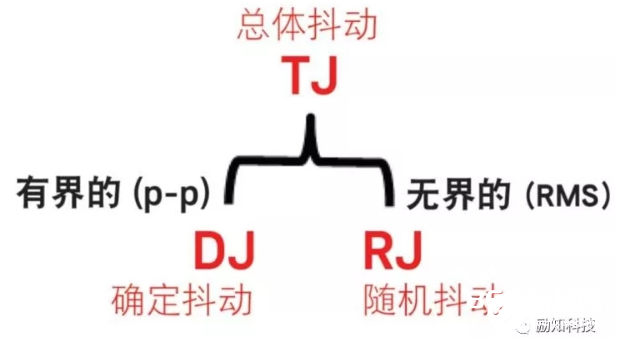

存储器速度的进步,也导致随机颤动爆增。DDR4 是第一款速度超快而有必要将颤动操控在规则范围内的 DRAM。过多的颤动会削减数据有用窗口,所以有必要明晰界说 DDR4 的数据有用窗口。

DDR4 器材开发人员所重视的另一个问题是互操作性。其最终方针是保证存储器体系的通用功用,一起进步功率和出产力。唯有明晰地了解 DDR4 标准的测验要求(例如,存储器时序、眼图丈量和颤动)和测验进程(例如,正确的勘探和仿真协议),您才干康复裕量,缩短芯片/体系的规划周期、下降本钱并加速产品上市速度。最终方针是保证存储器体系具有通用功用,且到达更高能效和出产功率。

什么是颤动?

颤动是指信号的时序事情违背其抱负方位的现象。

DDR4测验要求

前几代 DDR 存储器的时序标准依据多种危险假定,其间最大的假定是,只需数据设置和坚持时刻契合标准,就能够完成完美的数据捕获。DDR2 和 DDR3 的数据速率较慢且裕量较大,其标准假定随机颤动可疏忽不计且比特误码率(BER)为零。当然,它实践上并不为零。关于时钟颤动,丈量 10,000 个周期的时钟周期,其误码率将为 1e-4,因此能够以为它满意挨近零。DDR2 和 DDR3 较低的数据传输速度使得这些假定能够建立,由于在体系发现不合格成果之前存在满意的裕量。

DDR4 的数据速率更快,这会下降裕量,随机颤动或许会快速封闭数据眼图,这意味着误码率会添加。假如不加以操控,有或许会发生严峻的体系牢靠性问题、延伸设计时间、减缓产品上市时刻并添加规划周期的本钱。但是,DDR4 测验要求能够正面地处理这些问题,保证牢靠性并下降本钱。

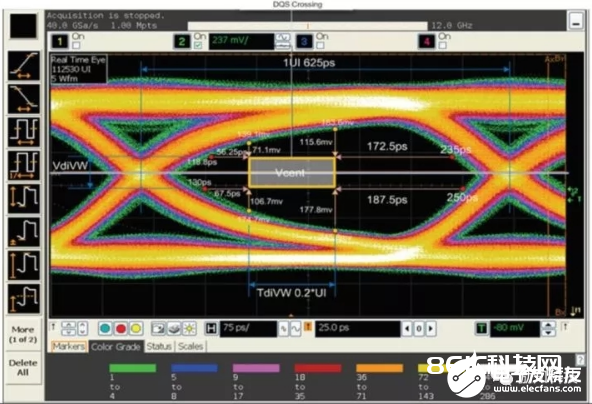

将捕获的波形数据显现为实时眼图(RTE),能够深化了解串行数据信号中的颤动。眼图基本上是数字化比特的叠加,显现比特何时有用(高或低)。它供给了描绘体系物理层特征质量的组成图画,并使峰峰值边际颤动和噪声得以具体显现。

实时眼图测验履行眼高和眼宽丈量,检查信号完整性并预估数据有用窗口。但是,仅丈量数据眼图并不能彻底了解数据有用窗口或预估比特误码率。现在,DDR4 标准的信号完整性丈量的是最差状况下的时刻裕度(tDIVW)和电压(vDIVW)。

眼图模板测验是最重要的物理层丈量之一,可用于测验整体信号完整性。从整体颤动能够推导出与眼图模板相关的最小时刻和最小电压的裕量。假如界说的 BER 很大(或许假如存在少数数据),就能够直接履行丈量。假如测验的 BER 很小,那么丈量数万亿个单位间隔(UI)就会花费太多时刻。

眼图模板测验可保证数据眼图不会超越或许发生颤动(和误码)的模板鸿沟。除此之外,它能够经过 tDIVW 丈量成果(图 1)陈述最小裕量(模板四个角的四个时序点)。

图 1. 眼图模板测验能够保证信号不会超越模板鸿沟(在鸿沟上或许发生颤动和误码)。

眼图测验

–能够丈量数据眼高和眼宽

–用户还能够依据器材标准界说自己的眼图模板

–假如眼图不契合模板,那么一致性运用软件能够陈述不合格状况

DDR4 标准考虑了颤动和 BER 的要害作用。核算颤动 BER 丈量成果很重要,它能够核算丈量整体颤动(确认性颤动+随机颤动),了解规划的数据有用窗口成果和或许呈现过错的概率。

除了标准测验,选用正确的测验进程和办法也是至关重要的。例如,示波器探头的正确放置会影响一致性测验成果以及规划裕量的精确表征和测验。关于 JEDEC 标准,最佳勘探点坐落 DRAM 封装的球上(不在传输线或通道上,也不在存储器操控器上)。

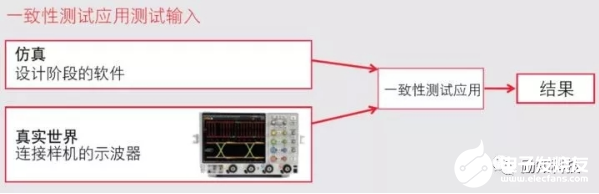

仿真是测验进程中的另一个重要却经常被疏忽的进程。跟着总线速度的进步以及取得尽量多裕量的需求,仿真进程能够很大程度地协助削减规划周期和本钱。

例如,仿真有助于保证体系能够忍受内插器的负载效应。这一进程评测所丈量的带宽/频率响应,保证内插器不会断开总线。

最终,是德科技与 JEDEC 安排亲近协作,以保证其测验和丈量处理方案与 JEDEC 标准的测验和丈量标准坚持高度一致。

图 2. 然后将具有恰当负载效应的仿真规划与原型的实践扫描成果进行比较,确认体系正常运转。

技能洞悉:核算整体颤动

确认性颤动(DJ)通常是有界而可猜测的,能够与数据流相关联,例如符号间搅扰和占空比失真。随机颤动(RJ)归于高斯散布并且是无界的。与任何高斯散布相同,跟着总量的添加,散布的峰-峰值也会添加。因此,整体颤动(TJ)等于确认性颤动 DJ 加上随机颤动 RJ 与 BER 的乘积。了解颤动的组成和来历能够协助规划人员下降规划中颤动的发生率,保证更好的数据功用。

物理层 DDR4 测验的处理方案

精确履行测验的三个进程:

挑选适宜的探头并把它置于正确的方位

挑选能够履行恰当运用剖析的示波器

运用契合 JEDEC 标准的主动一致性测验运用程序

1. 挑选适宜的探头并把它置于正确的方位

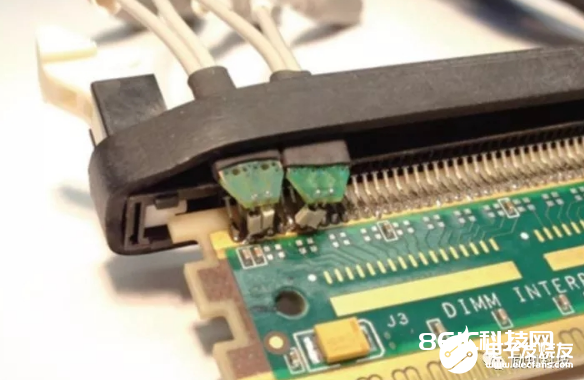

关于选用 DDR4 存储器的核算机体系规划,有几种勘探办法能够拜访用于测验的存储器体系。第一种勘探办法适用于核算机体系有内存插槽/衔接器,能够刺进DIMM 或 SODIMM 的场景。关于此类装备,拜访信号的最简略办法是运用插槽内插器(图 3)。

图 3. SODIMM 插槽内插器

插槽内插器将一切指令信号路由到电缆,该电缆能够替代 MSO 电缆而直接衔接到混合信号示波器(MSO)的输入端。拜访数据选通信号(DQS)和输出数据(DQ)时,探头前端能够焊接到插槽内插器上并衔接到模仿通道(图 4)。这样就能够检查 SODIMM 的 16 个数字通道以及经过模仿通道传输的 DQS 和 DQ 信号。

图 4. 运用焊入式探头前端能够拜访路由到示波器模仿通道的 DQS 和 DQ 信号。在本例中,咱们运用的探头前端是 E2677A。

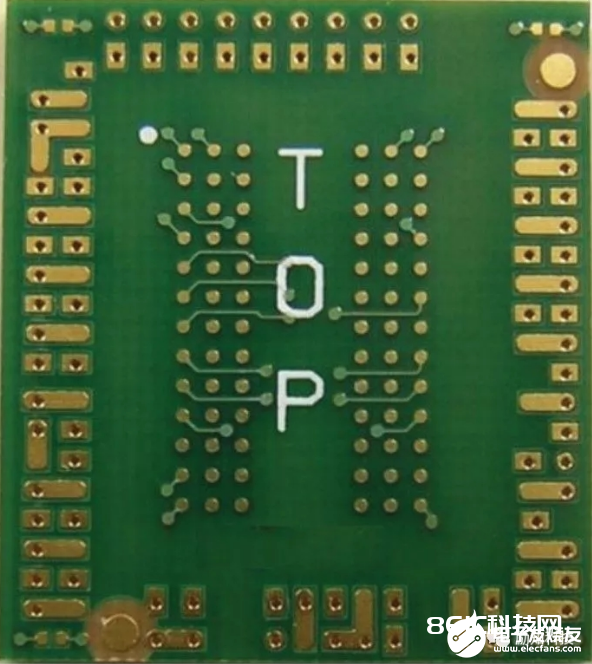

另一种挑选是 DDR4 BGA 勘探,它适用于测验嵌入式体系(或 DIMM 装备)。对 DDR4 而言,BGA 内插器的规划意图是供给拜访一切信号的途径,以便在表征一切信号(数据、地址、操控、指令、选通和时钟)时完成最大的灵敏性。运用这种勘探办法时,需求将 BGA 内插器焊接在 DRAM 和电路板之间。衔接示波器的焊点坐落 BGA 顶部(图 5)。

图 5. Keysight DDR BGA 内插器。经过内插器周围的示波器焊点拜访信号。

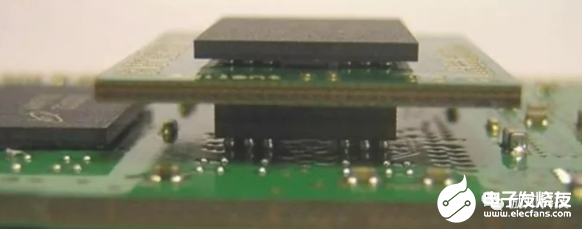

假如空间特别狭小(特别是在 DIMM 装备中),或许需求转接器将内插器从电路板上架高,这样它就不会搅扰任何相邻的元器材(图 6)。在这种状况下,转接器将焊接在内插器的底部。

图 6. DDR BGA 内插器配有一个转接器,用于在表面积较小的区域内架高内插器。

定制内插器

假如您需求一款内插器,而咱们现有的规划无法满意您的需求,那么咱们的规划团队能够与您协作创立定制处理方案。请与是德科技协作以发动这一流程,或拜访:www.keysight.com/find/contactus。

2. 挑选能够履行恰当运用剖析的示波器

确认勘探协议之后,下一个要害的考虑要素是挑选测验设备。虽然存储器技能的 BER 标准才刚拟定,但这种测验已然老练运用于高速规划,并得到相应丈量东西(如示波器)的支撑。运用具有先进丈量剖析功用的示波器非常重要,这些功用包含去嵌入、实时眼图丈量、混合模仿和数字信号;以及穿插参照仿真规划等。

MSO 示波器是一种能够一起显现和剖析数字和模仿信号的仪器。MSO 的一个优势是能够别离读写数据。用户能够将指令总线、行地址选通(RAS)、列地址选通(CAS)、写入激活(WE)、片选(CS)和时钟信号衔接到数字通道,使示波器依据这些信号中的恣意信号或信号组合触发读指令或写指令。它能够别离相应的数据并履行电子和时序测验。MSO 还答应测验人员检查指令协议的流程,检测协议是否违规。

挑选示波器时,有必要要了解它与其他规划和测验东西怎么整合。是德科技运用其作为国际闻名电子丈量公司的共同方位,精心构建先进的 EDA(软件仿真)东西和示波器。当在 DDR4 规划的最终阶段运转传统的电子和时序标准时,是德科技的东西套件供给了共同的优势,能够对候选版别中的仿真波形和物理原型的波形丈量成果履行彻底相同的一致性测验。换句话说,仿真波形能够导入示波器中,与从物理原型取得的波形进行比较。

仿真进程能够明显削减规划的迭代次数和本钱。每次履行勘探时,都会给体系添加额定负载。仿真该负载可保证内插器不会损坏总线或发生任何不知道负载。Keysight W2351 DDR4 一致性测验台可用于仿真负载效应并生成去嵌入文件,然后消除勘探效应并运用示波器进行丈量(关于去嵌入的具体信息,请参阅下一页的进程 3),这样就能够真实地将您仿真的规划与原型进行比较。

Keysight Infiniium V 系列示波器

Keysight Infiniium V 系列示波器针对高速 DDR 存储器丈量进行了优化。V 系列供给业界较低的本底噪声和颤动丈量本底以及较高的有用位数(ENOB),因此成为发射机信号完整性丈量的抱负东西。供给从 8 GHz 至 33 GHz 的各种类型,并可晋级其带宽以满意您未来的需求。它与 InfiniiMax III 和 III+ 勘探体系结合运用,能够供给更精确的丈量,满意更严苛的规划裕量要求。别的,它还供给 16 个数字通道,时刻分辨率高达 50 ps。此外,凭借是德科技先进规划体系(ADS)和 DDR4 软件,您能够直接将仿真成果与示波器软件测得的实践特征相关联。

需求问询示波器供货商的问题:

我能够穿插触发和丈量数字和模仿通道吗?

示波器是否具有去嵌入功用?

它是否具有实时眼图丈量功用?

我能够将它穿插引证到我的仿真规划中吗?

3.运用契合 JEDEC 标准的主动一致性测验运用程序

测验处理方案的最终一个组成部分是示波器软件。运用 DDR4 一致性测验运用软件(例如Keysight N6462A DDR4 电气一致性测验软件),您能够运用日常用于调试的示波器,依照 JEDEC 标准履行主动存储器测验和裕量剖析。每次测验时,该运用软件都会主动装备示波器,使其能够供给有用成果。它还包含裕量剖析,指示您的器材间隔各项标准的合格标准有多远。

一致性运用软件还应具有某种“自界说”形式,能够包含包含眼图剖析、模板测验和振铃在内的要害丈量。这些丈量对表征 DDR4 器材至关重要。

Keysight DDR4 一致性测验运用软件可测验 JEDEC SDRAM 标准中规则的时钟、电气和时序参数。该运用软件能够协助您运用 Keysight Infiniium 示波器测验一切 DDR4 和 LPDDR4(低功耗)器材的一致性。

是德科技的运用软件还能够供给具体的陈述,包含用屏幕快照显现的最差状况值,以及依据标准确认的丈量成果的合格/不合格状况。它还能够核算间隔标准合格线的裕量。用户能够添加运转次数,搜集更多数据进行核算剖析。核算陈述将显现测验的最小值、最大值和标准差。这些数据在比较 DRAM 供货商或不同客户的测验成果时特别有用。

Keysight DDR4 电气一致性测验软件陈述包含:

1.运用屏幕快照显现的最差状况值

2.合格/不合格状况以及间隔该标准的裕量

3.屡次试运转成果

4.包含最小值、最大值和标准差的核算陈述

技能洞悉:InfiniiSim

Keysight InfiniiSim 波形转化东西套件供给更灵敏、更精确的办法,来显现数字串行数据链路中恣意处的波形。高度可装备的体系建模能够简略快速地帮你消除剩余通道元素的有害影响,仿真刺进了通道模型的波形,检查物理上无法勘探方位的波形,补偿探头和其他电路元件的负载效应。最终方针是在依据标准进行测验或履行表征作业时取得更多裕量。

Keysight DDR4 电气一致性测验软件的优势:

是德科技积极参与 JEDEC 安排的各项作业 — 在 DDR4/LPDDR4 BER 测验办法上做出了要害奉献

比竞争对手更多的测验覆盖率

DDR4 一致性测验处理方案的一站式商铺(软件+ BGA 内插器)

经过 W2351 一致性测验台软件穿插引证并仿真运转

Infiniisim 波形转化东西套件

总结

DDR4 的速度要求以新的办法界说和丈量要害的 AC 时序参数(例如数据输入有用窗口的时序和电压)。示波器装备的勘探剖析东西与主动一致性测验相结合,能够保证测验成果的可重复性和牢靠性。

规划人员若想缩短学习时刻,赶快把握新一代测验与丈量协议的常识,那么最好考虑与积极参与 JEDEC 标准委员会作业的测验东西厂商协作。经过亲近的协作和交流,规划人员能够找到更新、更好的一致性测验处理方案。这关于新发布的技能特别重要,由于其标准和丈量办法依然处于评论进程中。

Keysight DDR4 眼图概括测验办法现在得到 JEDEC 的采用,用于 DDR4 标准化作业。是德科技仍是一家在 DDR 芯片开发一切阶段均供给硬件和软件处理方案的测验与丈量公司。从仿真到调试,从验证到一致性测验,是德科技的处理方案都发挥了重要作用。

任何从 DDR 存储器规划的技能人员都面临着在不断缩小的封装中完成更快存取速度和更低功耗的继续压力。在产品规划阶段尽早洞悉您的规划,能够快速采纳纠正办法,保证您的产品到达质量、互操作性和上市时刻等方针。成功的规划取决于功率以及缩短规划周期,操控规划本钱。走运的是,今天有许多东西能够协助您完成这一方针。