最近接了一个项目吧,是咱们校园物理院院长带的研究生搞的,小墨有幸跟他们协作,担任FPGA方面的作业,完结后听说还会请求国家专利,详细到什么时分完结,那或许便是驴年马月了,或者说我现已不在校园了。从今日开端,小墨将开端触摸赛灵思公司的FPGA(教师供给的渠道),用到的当然是SOPC。其实做做项目也好,让自己训练一下,我也好久没有做大一点的项目了,对我来说也是一个时机吧。

信号发生器这个东西信任咱们都知道,关于根据DDS信号发生器的技能文档网上也多的是,但是我仍是想写一下这部分的教育,因为从我本身的学习来看,这部分内容并不是很难,也很简略完结,代码也就那几行。但是,我发现我其时学这部分的时分,从网上找材料,大部分都是根据原理的解说,或者说仅仅做到仿真这一步,并且原理的解说过分书面化,初学者不怎样好了解。我做了这么一个教程,全方面的做一个这样一个体系。其间包含信号发生器的原理部分,代码完结,仿真,按键操控频率、相位改换,包含正弦波、方波、锯齿波、三角波的发生,以及D/A转化芯片的操作,直到能够在示波器上调查到咱们发生的波形,并经过按键操控停止。

这个体系的规划大约花了我三四天的姿态,写的也是蛮用心的,工程不是很大,但仍是有些细节需求留意的,下面咱们就一步步的开端做。

一、全体结构

关于原理部分,书上讲的许多,但是总是感觉不尽人意,过于书面化的言语让人看着很头疼,下面就让小墨来给咱们解说,期望给读者带来一种眼前一亮的感觉,让你再回去看书,看代码的时分觉得称心如意了。

首要咱们应该先清晰要做什么,咱们要做的是一个频率,相位可调,恣意波形信号发生器,也便是咱们常见的正弦波,方波,锯齿波,三角波等。

其次,咱们需求知道咱们需求哪些参数。比方,咱们要生成一个正弦波,它的初始频率是多少,相位是多少,步进频率、相位是多少,怎样核算这些参数?

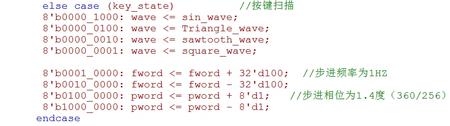

然后咱们需求知道怎样生成一种波形,怎样样经过按键完结波形与波形之间的转化,例如我按下一个键生成正弦波,再按下一个键生成三角波,怎样完结?

再然后,咱们需求把生成的数字信号送入D/A转化芯片,D/A转化的接口怎样写?怎样确保收集的数字信号完全正确?

最终,咱们能够经过示波器调查咱们生成的波形信号,验证咱们的频率,相位是否契合咱们的规划要求

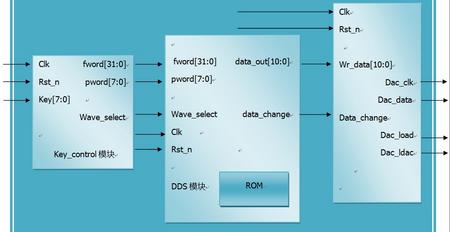

下面是我简略的做的一个结构图

下面咱们先来解说一下上面这张结构图。

首要,咱们经过8位按键挑选输出何种波形,这时分wave_select信号被赋予相应的值送给DDS模块,DDS模块由wave_select信号,从ROM中挑选适宜的地址,地址每改动一次,也便是数据每改动一次,DDS模块会奉告DAC模块数据发生改动了,让它留意数据的收集,不要采错了!一同能够经过按键操控模块调理输出信号的频率,相位等,DAC模块将收集到的数字信号转化成模拟信号,送到示波器上显现。留意DAC芯片的采样频率,DDS信号的输出频率不能大于收集频率,不然数据就会犯错。

二、DDS信号发生器原理详解

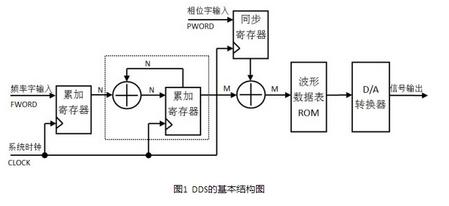

关于发生器原理这样部分有必要好好讲讲,许多人仍是对某系问题不得其解,先来看这张图

DDS根本的结构组成,看图就知道了,包含相位累加器,相位调制器,波形数据表,和DA转化。咱们还能够看到有两个输入,即频率操控字输入fword 和相位操控字输入 pword,这两个输入便是咱们用来操控输出波形频率和相位的

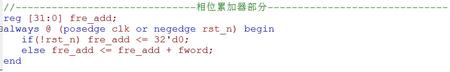

1、相位累加器

相位累加器的原理,咱们先假定频率操控字fword 为1。相位累加器的原理便是先将fword的值送到相位累加器,然后每来一个时钟,相位累加器的输出值,就跟相位累加器的新输入值相加,之后再送入相位累加器,再来一个时钟,再跟输入值相加送进去,如此循环。例如刚开端fword = 1 ,那么第一个时钟周期相位累加器的输出便是1,第二个时钟周期输出的便是2,第三个时钟周期输出的便是3。再例如,咱们的频率操控字fword 刚开端等于2,那么相位累加器输出的就依次是0,2,4…..也便是说频率操控字fword 越大,相位累加器的输出值距离也就越大,那么咱们假定相位累加器的输出是32位的,假定fword越大,那么频率操控字记完到2^32 的时刻就越短。这样的话,咱们来算一下

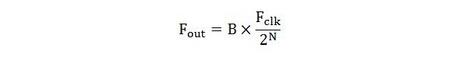

咱们运用的是50M的晶振,周期为20ns,假定fword为1,相位累加器的输出为N位的,那么每20ns,相位累加器加1,要加到2^N,需求20ns x 2^N 时刻,这个时刻便是输出一个完好信号的周期,那么咱们能够知道,输出信号的频率为 Fout = Fclk /2^N,其间,Fclk为咱们的晶振频率,再假定,fword = B 的时分,相位距离进步 B 倍,因而计满一个周期的时刻缩小了 B 倍,频率进步的 B 倍。综上所述,咱们得出了输出信号的频率核算公式

有了这个公式,那么,假定咱们把2^N看成是一个周期波形的相位,也便是说把一个波形的相位均匀分红2^N个,每一个相位对应一个数字信号,将这些数字信号送到DA转化芯片,转化成模拟信号,不便是咱们的信号发生器了吗?

好,这儿咱们假定N = 32 ,也便是把一个波形的相位分红了2^32个点,但是位数越多当然占用的资源也就越多,不能取那么多,怎样办呢,咱们只取它的高8位即可

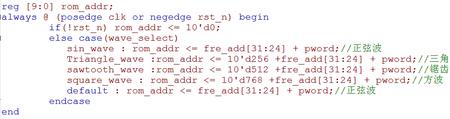

即取fre_add[31:24] ,将这8位数送给ROM的地址。许多人不明白了,为什么这样取8位,这样取8位不是把一个完好的信号给切断了吗?刚开端我也有这么想过,但是细心算一下才知道自己是多虑了。用核算器算一下知道,2^32 = 4.3x 10^9 左右,而2^24 = 16 x 10^6 左右,前后差了几个数量级,所以,咱们取fre_add[31:24],相当于把一个波形的相位分红了256个点,每个点对应一个数据。

二、ROM

上一部分说了,咱们将一个波形分红了256个点,每个点对应一个数据,那么咱们怎样完结呢,这儿就要用到咱们的只读存储器ROM了,咱们能够先把波形的数据送到ROM里存起来,然后再从中取,取的地址便是咱们的fre_add[31:24]这8位数,由此看来,fword越大,这256个地址取址的距离就越大,相应的波形频率也就越大了,当然,咱们的ROM不但存储一个波形,咱们能够把ROM设大一点,里边放多种波形,再经过按键进行相应的选址,然后输出各种波形

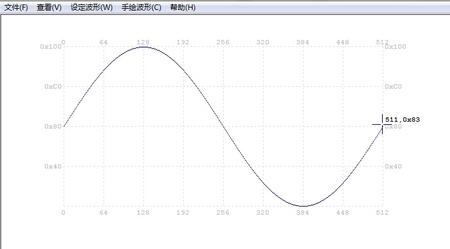

提到这儿有些人该问了,怎样将数据送到ROM里去呢?这个的话就规划到mif文件的制造,详细怎样做咱们仍是自己回去补课了,纷歧一介绍了,但是我这儿有一个mif文件生成器,网上也有下载,能够生成各种波形,也能够进行相关参数的修正,留意保存的时分保存成.mif格局的文件即可,调用的时分在IP核 ROM的装备的时分调用就好了,但是要留意位宽。

三 、相位调制器

相位调制器部分就简略了,便是相位累加器取好的的8位ROM地址,咱们能够经过按键进行加加减减,然后操控ROM取址的不同,然后操控波形的相位

四 、参数核算

由上面的公式咱们知道了输出波形的频率核算公式,当fword =1的时分咱们算一下

输出频率 Fout = 50_000000 / 2^32 = 0.01,便是个大约值了,也便是说,在fword =1的时分,咱们的输出波形的频率为0.01HZ,假定咱们让波形初始化的时分输出的是一个100HZ的正弦波,那么,咱们应该设定fword = 10000,相位的话能够随意设置,咱们就默以为0相位好了。假定要进行频率,相位可调,咱们只需求让fword每次加100,就相当于频率步进为1HZ了,当然,因为咱们的地址是8位的,那么,步进的相位便是 360 /256,大约等于1.4度吧。

还有,已然频率为100HZ,也便是周期为0.01s,ROM要在0.01s内要输出256个数,那么每输出一个数的时刻为0.01 /256 大约为 39us的姿态,因而,咱们的DAC的收集频率不能比ROM的输出频率小了,不然的话收集到的数据是不精确的

综上所述,咱们总结一下

输出频率: 100HZ

输出相位:0

步进频率:1HZ

步进相位:1.4度

DAC收集时刻:小于39us

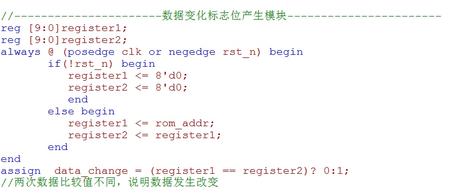

当然在一般状况下 DAC的收集频率是远大于ROM的输出频率的,只需信号输出频率不是特别快,收集正确仍是有确保的。为了确保收集的正确性,我特别加了一个数据改动检测部分,一但数据发生改动,就奉告DAC模块,做相应处理

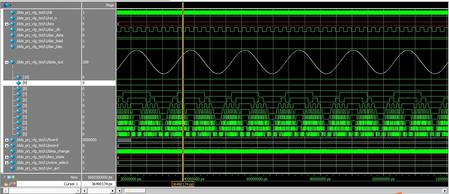

悉数准备就绪,咱们能够做一下仿真,详细的仿真调试进程不做详解,仍是咱们自己着手去做的进程

五、DAC接口电路

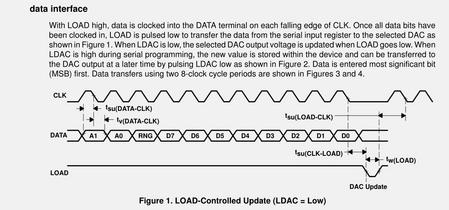

DA芯片我用的是TLC5620这块芯片,这块芯片是四路输出,8位的的数模准换芯片,芯片的操作不是很难,咱们仍是先来看一下芯片的datasheet

DA芯片有这几个管脚需求用到,分别是

dac_clk,用于发生DAC的作业时钟,阐明文档上说时钟最大为1M,而咱们的晶振为50M因而咱们需求做个分频,我做了个64分频,当然是为了安稳,假定能够咱们也能够试试更高的频率

dac_data , 是串行输入的接口,用来接纳数字信号

dac_load ,将接纳来的数字信号开端转化成模拟信号的使能端,低电平有用,要继续最低250ns

dac_ldac , dac信号改写操控端,当dac为低电平的时分一向有模拟信号输出,不然不再改写

上面那个时序图大体解说一下,便是在load信号是高电平期间,每来一个DAC作业时钟的下降沿,就将1位数据经过dac_data端口送到DAC芯片内部的移位寄存器中,寄存器是11位的,前两位为输出模拟信号的通道号,第三位是用来核算输出电压用的一个参数吧,低8位是输入的数字信号,当移位寄存器存满之后,给一个load信号,作业时钟处于不作业状况,留意,这一点很重要,我其时便是不知道这一点,一向调欠好,便是在转化期间,让作业时钟处于非作业状况,等候250ns之后,将load拉高,进行下一次收集。

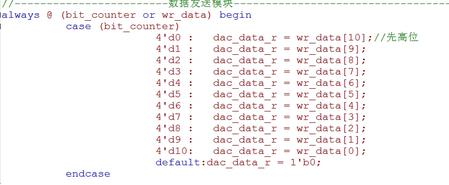

关于代码的剖析这儿也不做详细剖析了,咱们仍是自行消化,这儿只传一部分,关于数据的发送部分的代码

每来一个时钟,送一位数据给dac_data端口,送满移位寄存器停止,当移位寄存器计满的时分,load拉低,一同时钟停止作业,bit_counter 清零,等候下一次收集。当然当数据发生改动的时分,也便是data_change 信号来的时分,bit_counter 也清零,从头收集,防止收集过错

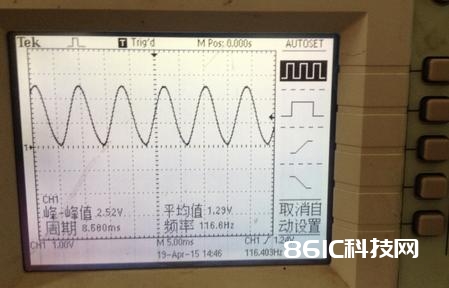

悉数模块编译完结之后,咱们就能够用示波器来检测咱们的成果了

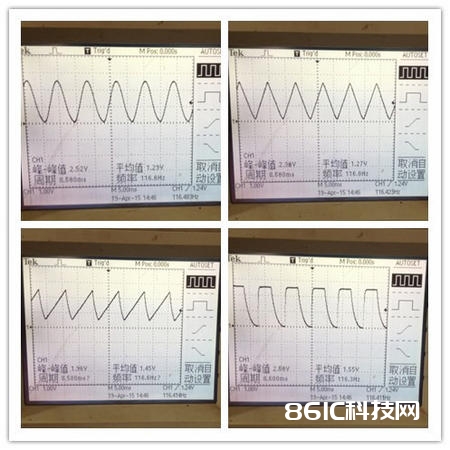

由示波器的成果咱们能够看到,输出电压峰值为2.5V,当然这是由芯片决议的,输出频率为116HZ,大体契合咱们的要求,究竟咱们许多参数做了近似,再经过按键进行波形的改换,发现各波形输出正常,只要方波和锯齿波,在电压下降的时分改动有点缓慢,当然这也得考虑咱们芯片的要素,究竟电压不能改动的那么快,也归于正常状况

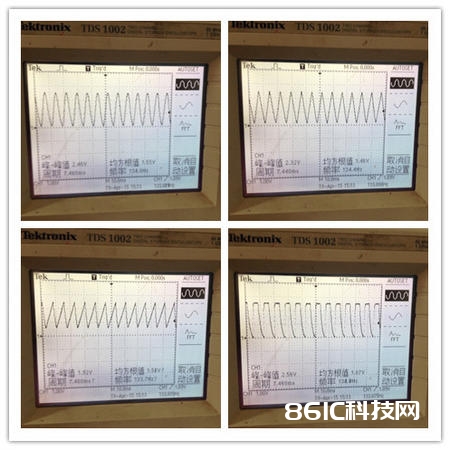

波形显现正常,下面经过按键来调理波形的频率和相位,但是完结实时显现的功用,发现频率,相位都有所改动

当然,这个工程也有做的欠好的当地,例如,再进行相位调理的时分,因为各种波形的地址在ROM里边是挨在一同的,这样进行相位调理会侵略其他波形的地址,这一点我其时也考虑过了,短时刻内没有想出更好的方法,能够用多个ROM,其他的方法还请咱们自己动脑子想一下吧,想出来了能够给我留言,咱们一同沟通嘛

好了,这一次首要仍是讲了一下工程的全进程,没有细心讲代码编写的详细进程,也没有讲仿真时分的操作流程,这些部分仍是留给读者渐渐去探索,究竟这也是一个学习的进程,今日就到这儿吧,因为小墨手上也有了项目,平常还要上课,更新速度方面应该不是很快!谢谢咱们的支撑~