现在首要的代工厂都在出产FinFET晶体管,这些FinFET以创纪录的速度完成了从规划到现货产品的改动。FinFET的展开遍及一直都比较稳定,因为与平面器材比较,它们可以供给更低的功耗、更高的功能和更小的面积。这使得FinFET对智能手机、平板电脑及要求长电池寿数和高功能的其他产品来说极具吸引力。

当Intel初次在22nm节点运用FinFET时,他们宣称与bulk、PDSOI或FDSOI比较,FinFET在相同的总功耗条件下功能高出37%,或许在相同速度条件下功耗低50%。这些数据十分有吸引力,并且在向14nm及更小工艺节点展开时还有进一步改善的空间。

图1. FinFET的功能,功耗和面积优势

在运用功耗方面,操控功率走漏关于平面器材,特别是在较小的节点来说,已然成为了一项艰巨应战。经过抬升沟道,包裹沟道四周的栅极,FinFET可以创立一种彻底耗尽型沟道,然后战胜平面晶体管的漏电流问题。FinFET所具有的更好的沟道操控才能可以用来完成更低的阈值和供电电压。

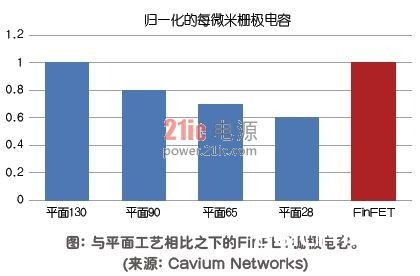

尽管漏电流在FinFET中是受控的,但动态功耗占总功耗的很大部分。与平面晶体管比较,FinFET具有更大的引脚电容,因而会导致更高的动态功耗值。据CaviumNetworks描绘,“与28nm工艺比较,FinFET的每微米栅极电容提高了66%,与130nm平面节点的水平适当。”平面器材和FinFET器材的栅极电容值比较如图所示。

图2:与平面工艺比较之下的FinFET栅极电容。

那么这对规划工程师来说意味着什么呢?从完成视点看又会对规划流程形成怎样的改动?动态功耗(也称为开关功耗)在优化进程中应成为一个价值函数,有必要在流程的一切阶段加以充分考虑。

FinFET增加了物理规划流程的复杂性。更严厉的规划规矩和FinFET工艺要求(比方具有电压阈值认识的距离规划、植入层规矩等),都将对归纳、布局、底层规划和优化引擎施加束缚,然后直接影响规划的方针。一起因为FinFET是在16nm/14nm工艺完成,多重图画技能将主动成为运用FinFET的任何规划的一部分,这又增加了另一层的复杂性。

针对FinFET的规划主动化技能需求具有FinFET认识,以下降开关功耗,并供给具有功耗认识的RTL归纳、活动驱动型布局和优化、时钟树归纳(CTS)功耗下降以及并行优化动态与走漏等功能。功耗优化需求从规划流程的前期开端,架构挑选需求具有功耗友爱特性,以便保证规划在完成时具有最低的功耗。

数字完成进程是从RTL归纳开端的。因为FinFET被应用于最新、最大的规划,RTL归纳引擎有必要具有在合理运转时刻处理1亿个以上门电路的才能。当然,它还有必要供给高质量的成果,这可以在考虑芯片的一切要素后在全芯片级履行RTL归纳来完成。履行多个具有不同规划束缚条件的归纳使命来探究不同规划计划也是很有用的。可以调查规划方针怎么相互影响有助于在满意功耗、功能和面积方针要求方面做出聪明的折中计划。

为了满意功耗方针,完成流程需求从归纳开端并贯穿整个物理规划流程,采纳一系列的降功耗战略。最常见的战略包含多阈值库、时钟选通、多旮旯/多形式(MCMM)功耗优化、引脚交流、寄存器会集、重映射和功率密度驱动型布局。RTL级功耗剖析关于剖析和修正规划流程前期呈现的功耗问题来说十分重要。

在RTL和地图之间穿插检测的才能也有助于在规划流程前期辨认和调试问题,并最大极限地减小最终一刻才发现问题的概率。

在先进节点运用FinFET的规划完成东西有必要在与各家代工厂的严密协作下得到增强和更新。在代工厂、EDA公司和两边客户之间要展开很多的工程技能协作,以便芯片规划人员可以充分发挥每种新工艺节点的优势。