5.3.3.2 进步时序功能的手法

时序功能是FPGA 规划最重要的目标之一。形成时序功能差的根本原因有许多,但其直接原因可分为三类:布局较差、逻辑级数过多以及信号扇出过高。下面经过时序剖析实例来定位原因并给出相应的解决方案。

1.布局太差及解决方案

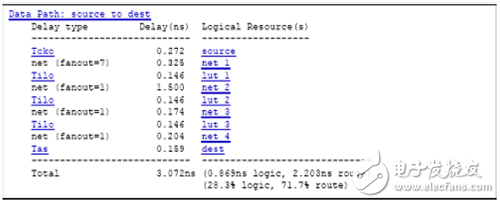

图5-13 所示时序陈述,其间附加的周围束缚为3ns,实践周期为3.027ns,逻辑时刻只要0.869ns,而布线推迟竟到达2.203ns,很明显失利的原因便是布局太差。

图5-13 布局太差的时序陈述示意图

相应的解决方案有:

1) 在ISE 布局东西中调整布局的尽力程度(effort level) ;

2) 运用布局布线东西的特别尽力程度(extra effort) 或MPPR 选项;

3) 假如用户了解区域束缚,则运用Floorplanner 相对区域束缚(RLOC),从头对规划进行布局规划。

2.逻辑级数过多及解决方案

在FPGA 规划中,逻辑级数越高,意味着资源的运用率就越高,但对规划作业频率的影响也越大。在图5-5所示的比如中,附加的周围束缚为3ns,实践周期为3.205ns,逻辑时刻为1.307ns,现已对规划的实践功能形成了必定的影响。关于这种状况,ISE 完成东西是没有任何改进的,有必要经过修正代码来进步功能,相应的解决方案有:

1) 运用流水线技能,在组合逻辑中刺进寄存器,简化原有的逻辑结构;

2) 查看该途径是否是多周期途径,假如是,增加相应的多周期束缚;

3) 具有杰出的编码习气,不要嵌套if 句子或if、case 句子,而且尽量用case 句子替代if 句子。

图5-14 逻辑级数太多的时序陈述示意图

3.信号扇出过高及解决方案

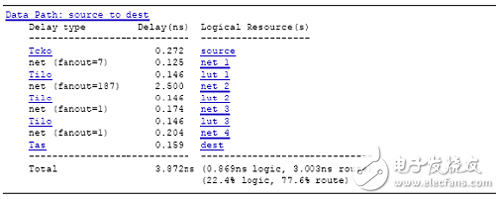

高扇出会形成信号传输途径过长,然后下降时序功能。如图5-15 所示,附加的周期束缚为3ns,而实践周期为3.927ns,其间网线的扇出现已高达187,然后导致布线时延到达3.003ns,占实践时延的77.64%。这种状况是任何规划所不能容忍的。

图5-15 扇出太高的时序陈述示意图

相应的解决方案有:

1) 经过逻辑仿制的办法来下降信号的高扇出,可在HDL 代码中手动仿制或经过在归纳东西中设置到达意图;

2) 可运用区域束缚,将相关逻辑放置在一起,当然本办法仅限于高档用户。