跟着现代电子技能的不断发展,在通讯体系中往往需求在必定频率规模内供给一系列安稳和精确的频率信号,一般的振荡器已不能满意要求,这就需求频率组成技能。DDS是第3代频率组成器,它选用全数字技能,具有频率切换时刻短、频率精度和分辨率高、输出相位接连、易于操控等长处。

现场可编程门阵列(FPGA)器材具有作业速度快、集成度高、可靠性高和现场可编程等长处,而且FPGA支持体系现场修正和调试,选用FP GA规划的DDS具有电路简略,功用安稳等特色,也能满意绝大多数通讯体系的运用要求。而在DDS相位累加器的规划傍边,传统的累加器选用多位全加器直接相加的办法来完结,但跟着频率操控字位数的增加,体系的实时性会大幅下降。针对这一问题,本文提出了一种流水线结构的相位累加器,该结构能够缩短运算时刻,进步整个体系的实时性。

本文介绍了DDS的根本原理,论述了依据流水线结构的累加器的规划方案及详细的规划办法,选用嵌入式逻辑剖析仪剖析了正弦波、方波、锯齿波和三角波等波形,并给出了核算机仿真和试验成果,最终总结了该体系的特色。

1 DDS根本原理

如图1所示,根本的DDS结构一般由4个模块构成,别离是相位累加器、波形存储器ROM,D/A转化器和低通滤波器LPF。

体系时钟fc为基准频率源,K为频率操控字,经过改动K的数值能够改动DDS的输出频率,在fc上升沿到来时,相位累加器会对频率操控字K进行相位累加,累加成果便是波形存储器ROM中幅值的地址数据,经过寻址,幅值由ROM输出到D/A转化器中,D/A转化器将由二进制编码的数字信号转化为模拟信号输出,该模拟信号再经过低通滤波器的滤波就能够得到滑润的波形曲线。

DDS的输出频率为:

fo=(K/2N)fc (1)

式中:N为相位累加器的位数;fc作为基准频率源一般是给定的数值,因而,决议DDS输出频率的要素别离是频率操控字K和相位累加器的位数N。当K取最小值1时,DDS的输出频率便是它的最小分辨率:

fo=fc/2N (2)

2 流水线相位累加器的规划

相位累加器是DDS的重要组成部分,在基准时钟操控下,它用来完结线性数字信号的逐级累加,信号规模从0加到累加器的满偏值,由此得到相应的相位数据,而相位累加器的频率便是DDS输出信号的频率。在一般的电路优化规划中,累加器模块选用超行进位加法器,这种结构克服了串行进位引起的时刻滞后,很大程度上进步了加法器的运算速度,但仍有缺乏。为了进步DDS频率转化速度和实时性,本文提出了一种流水线结构来优化DDS的相位累加器。

FPGA的结构特色很合适选用流水线规划,以Altera低本钱系列CycloneⅡ为例,不只有最多达68 416个逻辑单元(LE),每个LE均含有1个四输入查找表LUT、1个可编程触发器等。规划中可将1个算术操作分解成一些小规模的根本操作装备到LUT中,将进位和中心值存储在寄存器中,鄙人一个时钟内持续运算,整个体系只需求很少或不需求额定的资源本钱。

流水线结构的根本原理是将整个电路划分为若干个流水线级,每级之间设置寄存器锁存上一级输出的数据;每一级只完结数据处理的一部分,一个时钟周期完结一级数据处理,然后鄙人一个时钟到来时将处理后的数据传递给下一级。榜首组数据进入流水线后,经过1个时钟周期传到第二级,一起第二组数据进入榜首级,数据行列顺次行进。每组数据都要经过一切的流水线级后才干得到最终的核算成果,但对整个流水线而言,每个时钟都能核算出一组成果,所以均匀核算一组数据只需求一个时钟周期的时刻,这样就大大进步了数据处理速度。图2为在QuartusⅡ开发环境下用原理图输入法建立的流水线相位累加器结构图。该结构由四级流水线构成,每一级流水线的输入字节为8位,别离由8位数据锁存器,8位数据全加器,1位数据锁存器构成,整个体系可完结32位输入操控字的相位累加功用。依据流水线相位累加器的作业原理,首先将32位输入操控字a由低位到高位均匀分为4段,每一段为8位,别离以a[0..7]到a[24..32]来命名。将a[0..7]作为榜首级的输入操控字输入到8位数据锁存器reg8中,在时钟信号clk上升沿到来之时,reg8暂存的操控字会送入到8位数据全加器adder8中与另一个加法数和进位信号进行全加运算。另一个加法数是来自本级运算成果的反应,为坚持时钟节拍的一致性,该反应先输入到另一个reg8中暂存,然后在时钟上升沿到来之时输入到全加器进行运算;进位信号来自第四级,该信号也是先暂存在一个1位数据锁存器reg1中再输入到全加器中进行运算。

榜首级流水线经过全加器之后得出运算成果sum[0..7]和进位信号,sum[0..7]作为本级的输出,它是整个累加成果的最低8位,而进位信号经过一个reg1之后作为下一级全加器的输入。

第二级流水线的输入信号是a[8..15],因为上一级共由两级数据锁存器构成,所以在做全加运算之前先别离将输入信号和本级的反应信号经过2次数据锁存,然后再与来自上一级的进位信号进行全加运算,运算之后的成果作为本级的输出sum[8..15],一起发生进位信号参加下一级的运算。第三级与第四级的作业原理同上,体系每增加一级流水线结构,锁存器也会随之增加一级。

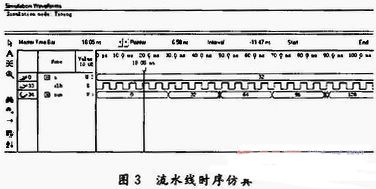

图3为在QuartusⅡ环境下得到的四级流水线仿真波形,时钟信号的频率是200 MHz,占空比为50 %,偏移量为0。为调查便利,输入操控字a和累加成果sum均用无符号十进制数来表明,且输入操控字设定为32,由波形图可见,该体系能够完结32位的相位累加。

3 恣意波形发生器的规划及完结

DDS能够依据ROM中存储数据的不同发生多种波形。在QuartusⅡ开发环境下建立DDS体系模型需求订制波形存储器ROM,依据所需精度的不同,ROM中存储的采样点数也不同。当所需波形数据十分简略时,能够在QuartusⅡ中定制ROM时直接将数据写入新建的mif文件,然后保存即可,当所需波形数据较为杂乱时,能够经过Matlab来主动生成所需波形的起伏数据,然后再经过调用mif文件来到达预期方针。以256个点的正弦波为例加以剖析阐明。

发生正弦波的Matlab程序如下:

width界说的是位宽,depth是深度,也便是将来生成的mif文件含有多少个存储单元,在此处,设定了数据宽度为8位,存储单元数为256,将来在QuartusⅡ中定制ROM时也要相应地将存储单元数设定为256,依据DDS的根本原理,跟着规划点数的增加,所得的波形数据会愈加精确,经过D/A转化后在示波器上观测的波形也越精准,但所需ROM的存储空间将会呈指数增加,所以要依据实践的需求来归纳考虑存储单元的个数。将上述指令在Matlab环境中运转之后就能够得到所需mif文件。

在mif文件生成之后需求将此文件增加进入DDS体系的ROM中,然后进行大局的编译,编译经往后就能够进行工程的下载。详细的波形能够经过示波器来剖析,或许运用Quartus Ⅱ自带的嵌入式逻辑剖析仪来剖析。在运用嵌入式逻辑剖析仪剖析和调查时,采样信号要依据DDS的时钟信号来确认,待测信号设定为DDS的输出信号,当工程下载到FPGA芯片后,待测信号经过USB-BLASTER反应至嵌入式逻辑剖析仪中,挑选不同的数据类型,能够调查到以十进制数据表明的数字信号或许以实践波形表明的模拟信号。

图4为在在嵌入式逻辑剖析仪中调查到的正弦曲线。由波形图能够看出,该规划方案能够完结正弦信号发生器的功用。依照相同的办法,修正发生mif文件的Matlb运算指令能够获得方波,锯齿波,三角波等波形。

图5~图7为能发生方波,锯齿波和三角波波形的工程文件下载到FPGA芯片后经过嵌入式逻辑剖析仪得到的波形图。由波形图能够看出,该体系能够完结恣意波形发生器的功用。

4 结语

本文将流水线相位累加器引进到DDS的规划中,使用电子规划主动化技能进行体系规划,并从嵌入式逻辑剖析仪剖析和调查了相应的波形,仿真和硬件试验验证了规划方案的正确性。该体系具有结构简略、运转速度快和占用芯片资源少等特色。跟着ROM查找表的扩展以及越来越多的直接核算波形数据的办法不断被提出,对DDS全体实时性的要求也越来越高,特别像现在较为盛行的cordic算法及改善的其它插值算法,因为算法自身跟着级数的增多,整个体系的频率转化功率就会下降,而流水线相位累加器结构能够很好地处理这一问题。