这是arm的时钟集成模块,首要想介绍关于arm的时钟系统.

S3C2440 有2个PLL(锁相环),一个是mpll,一个是upll

pll(锁相环)

是一种发生时钟频率的东西,一般发生时钟频率都是运用晶振(晶体振荡器),不过因为频率固定或许生产本钱高级一系列的原因,才发生出pll。pll合成器有外部晶体和对晶体的特定频率加班或许分频的集成pll电路。能够看出,pll能够在自身晶体的约束下自己diy要的频率,并且相对本钱也不会很高。

mpll会发生3中种时钟频率:FCLK,HCLK,PCLK

FCLK(CPU的频率):首要用于cpu核

HCLK:用于AHB(高速的外设总线)

PCLK:用于低速外围设备总线

upll用于usb外设

左上角的那个圈中的EXTCLK与OSC这两个是arm的时钟来历,EXTCLK是外部时钟,OSC是晶体。经过OM[2:3]来决议是用哪种方法;

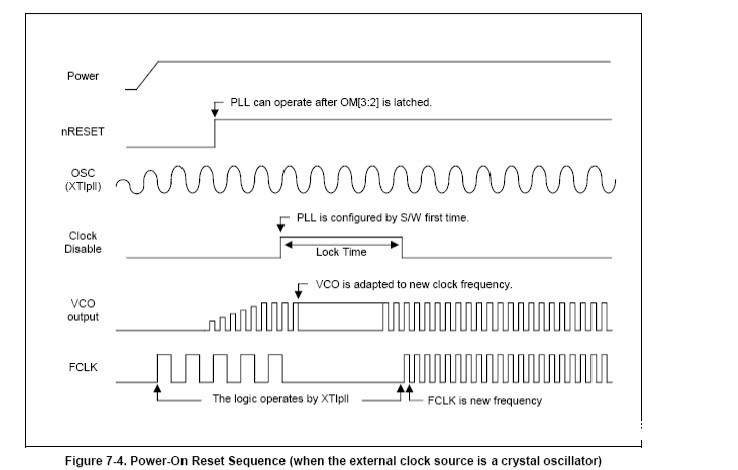

这幅图让咱们知道了arm时钟的发生来历,以及一系列的进程.

当arm通电的运用,FCLK不是有mpll来决议的,而是有FIN(外部输入时钟),当nRESET高电平的时分,PLL开端进行设置,这个时分OM[2:3]现已确定了,”PLL is configured by S/Y first time” 这个当地便是PLL的寄存器都现已被设置好的时分,至于LOCKTIME是什么,这个是PLL要输出安稳的频率所需求的时分,这个时分的FCLK为0,也便是cpu这个时分是不作业的。等locktime时刻玩了今后,咱们看到FCLK的频率就变的高许多,这便是cpu频率的来历。