rccresetandclockcontrol 复位及时钟操控

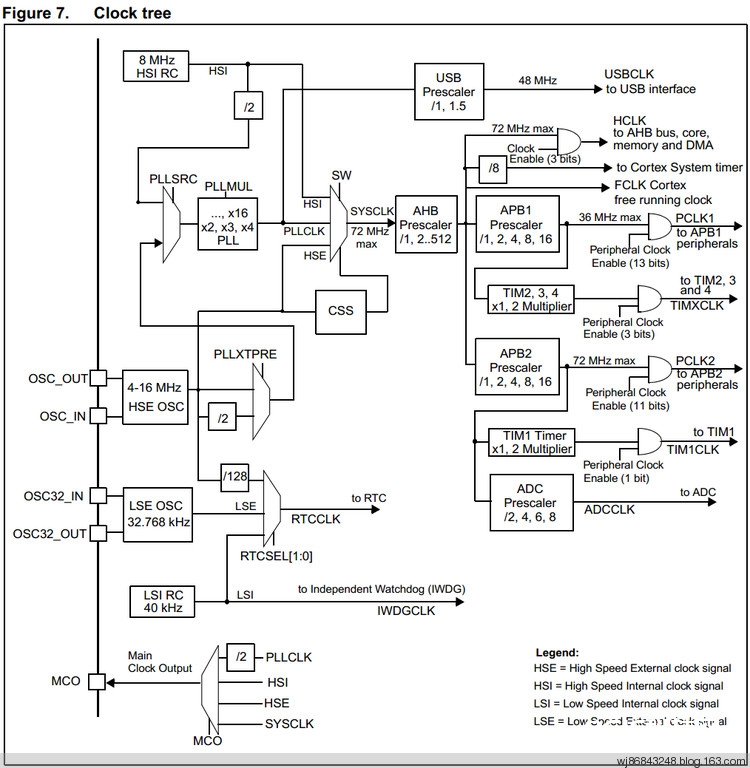

主要是设置时钟树中的内容,如下图所示:

详细在RCC_Configuration函数中的表现。

第一步:体系时钟挑选哪个,HSE、HSI仍是PLLCLK。

RCC_HSEConfig(RCC_HSE_ON); //运用HSE

假如HSE时钟现已安稳,硬件会将RCC_CR的HSERDY方位1。

第二步:判别HSE时钟是否安稳

if(RCC_WaitForHSEStartUp()==SUCCESS)

第三步:使能FLASH的预取址缓冲区,并设置FLASH的等候状况。(详细功用见FLASH部分)

/*EnablePrefetchBuffer*/

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

/*Flash2waitstate*/

FLASH_SetLatency(FLASH_Latency_2);

第四步:设置AHB预分频系数。预分频系数可所以1、2、4、8、16、32、64、128、256

/*HCLK=SYSCLK*/

RCC_HCLKConfig(RCC_SYSCLK_Div1);//没分频

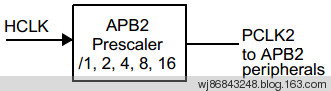

第五步:设置APB2的预分频系数,来确认PCLK2频率。预分频系数可所以1、2、4、8、16

/*PCLK2=HCLK*/

RCC_PCLK2Config(RCC_HCLK_Div1);//没分频

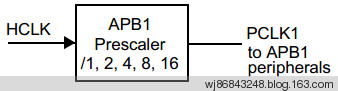

第六步:设置APB1的预分频系数,来确认PCLK1频率。预分频系数可所以1、2、4、8、16

/*PCLK1=HCLK/2*/

RCC_PCLK1Config(RCC_HCLK_Div2);//2分频

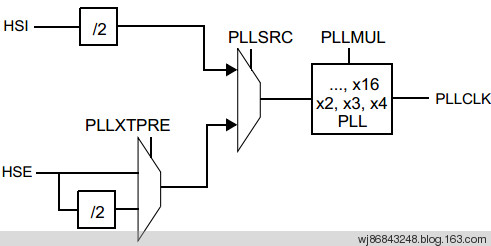

第七步:设置PLL的时钟源,以及PLL的倍频系数,来确认PLLCLK频率。

/*PLLCLK=8MHz*9=72MHz*/

RCC_PLLConfig(RCC_PLLSource_HSE_Div1,RCC_PLLMul_9);

第八步:使能PLL。将RCC_CR的PLLON方位1。

/*EnablePLL*/

RCC_PLLCmd(ENABLE);

假如PLL确定后,硬件会将RCC_CR的PLLRDY方位1。

第九步:等候PLL确定。

/*WaittillPLLisready*/

while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY)==RESET){}

第十步:挑选PLL作为SYSCLK(体系时钟源)

/*SelectPLLassystemclocksource*/

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

第十一步:将程序中用到的外设时钟翻开,一致都放在此处。

例如:将GPIO外设时钟翻开。

/* Enable GPIOC clock */

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOC, ENABLE);

RCC_Configuration函数详细代码如下:

/*******************************************************************************

* Function Name : RCC_Configuration

* Description : Configures the different system clocks.

* Input : None

* Return : None

*******************************************************************************/

void RCC_Configuration(void)

{

ErrorStatus HSEStartUpStatus;

/* RCC system reset(for debug purpose) */

RCC_DeInit();

/* Enable HSE */

RCC_HSEConfig(RCC_HSE_ON);

/* Wait till HSE is ready */

HSEStartUpStatus = RCC_WaitForHSEStartUp();

if(HSEStartUpStatus == SUCCESS)

{

/* Enable Prefetch Buffer */

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

/* Flash 2 wait state */

FLASH_SetLatency(FLASH_Latency_2);

/* HCLK = SYSCLK */

RCC_HCLKConfig(RCC_SYSCLK_Div1);

/* PCLK2 = HCLK */

RCC_PCLK2Config(RCC_HCLK_Div1);

/* PCLK1 = HCLK/2 */

RCC_PCLK1Config(RCC_HCLK_Div2);

/* PLLCLK = 8MHz * 9 = 72 MHz */

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);

/* Enable PLL */

RCC_PLLCmd(ENABLE);

/* Wait till PLL is ready */

while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET) {}

/* Select PLL as system clock source */

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

/* Wait till PLL is used as system clock source */

while(RCC_GetSYSCLKSource() != 0x08) {}

/* Enable GPIOC clock */

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOC, ENABLE);

}

}