依据SMIC0.18umCOMS工艺,规划一种宽频低功耗低相位噪声的CMOS压控振动器,电路选用差分LC振动器,一起选用堆集型MOS可变电容、缓冲电路及经改善的开关电容阵列,以降低功耗和相位噪声,由仿真成果可知,电路频率调谐规模为2.5G~3.1G,频偏为1MHz时相位噪声散布在-118dBc/Hz~-122dBc/Hz,作业电流小于10mA,满意规划要求,可运用于DRM/DAB接纳机。

DRM:全球数字播送体系(Digital Radio Mondiale)

DAB:数字声响播送(Digital Audio Broadcasting),即欧洲Eureka-147体系,是有些国家运用于电台播送的一项数字技能。

1.VCO在接纳中的运用

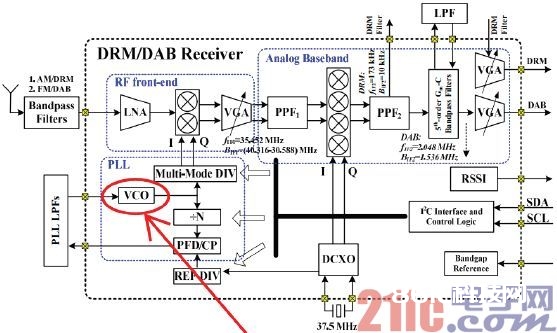

VCO在体系中的方位如图1所示,它归于环路部分,前级为环路滤波器,后级为多模分频器和可编程分频器。

图1 VCO在DRM/DAB接纳机中的方位

环路滤波器将PFD(鉴相鉴频器)和CP(电荷泵)发生的操控电压经过滤波之后供给给VCO。VCO依据操控电压(Vcon)和操控字(由I2C操控)发生相应频率的振动信号,此振动信号经过多模分频器器之后作为频率源供给给本地振动器(LO),一起也经过可编程分频器反应给PFD和CP。VCO输出的振动信号的频率为PLL输入信号(PFD/CP的输入)频率的N倍(N为可编程分频器的分频比),即fout=Nfin。

2.电路规划

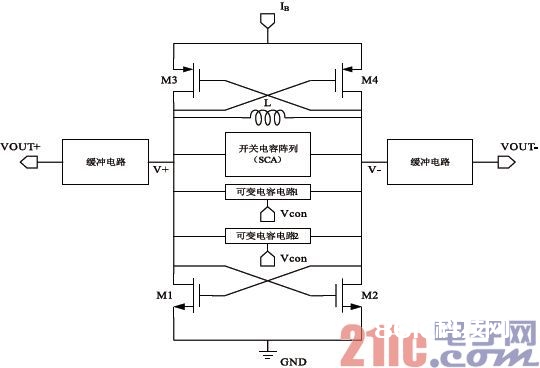

2.1 VCO电路图

图2所示为VCO的总电路图,选用经典的互补型差分耦合压控振动器结构,并将尾电流去掉,使相位噪声功能得到显着进步。M1和M2为NMOS差分耦合对,M3和M4为PMOS差分耦合对,选用互补型的差分耦合对更简单起振,具有功耗和振幅的优势,相位噪声也较小;开关电容阵列(SCA)用来拓展频率调谐规模而又不使压控增益过大;SCA由操控字来操控,对谐振腔中的电容进行粗调。可变电容用来在每一个操控字下对谐振腔中的电容进行细调。L即为谐振腔中的电感。缓冲电路用来将VCO的输出信号进行进一步扩大,以进步其驱动后级的才能,一起也将VCO和它的后级电路阻隔开来,防止VCO的振动频率和相位噪声功能受后级电路的影响。

图2 VCO总电路图

图2是互补型LC交叉耦合振动器,该结构一起选用NMOS和PMOS两对差分耦合扩大器供给负阻补偿谐振电路损耗的能量。关于相同的偏置电流和MOS管尺度,互补型结构供给的负阻是单对MOS管结构的两倍,电路起振更简单。因为NMOS对管和PMOS对管分别给对方供给电流,电流可以复用,增大振动器输出信号摆幅,而且经过优化器材参数使两输出端与中心电路节点上的输出电压波形对称,然后尽可能地减小振动器的相位噪声。

互补型LC交叉耦合振动器在输出信号起伏、功耗以及相位噪声等方面具有显着的优势。

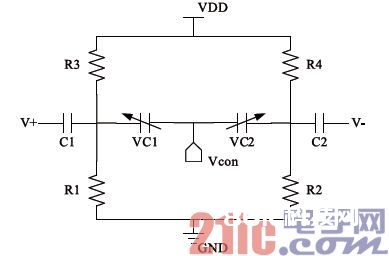

2.2 可变电容

本电路选用的是堆集型MOS可变电容,归于有源器材,运用时需加偏置电路。图3所示为可变电容的电路图,R1、R2、R3和R4为可变电容的管子供给偏置。C1和C2为隔直电容,使可变电容的偏置电路独立于其它电路,互不影响。Vcon为操控电压,是环路滤波器的输出,用来操控可变电容的电容值。

图3 可变电容的电路图

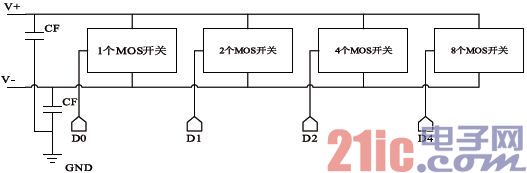

2.3 开关电容阵列(SCA)

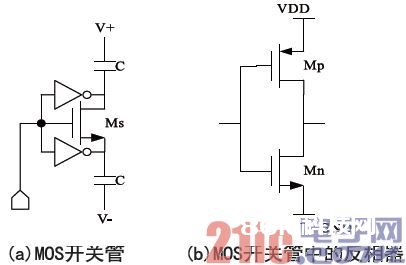

图4所示为开关电容阵列的电路,有四个操控字D0、D1、D2和D3,可以有16种组合。CF为滤波电容。图5所示为开关电容阵列中所运用的MOS开关管,在操控字端和源(漏)端之间参加反相器,数模混合,使MOS开关管的源(漏)极的电压有确认值(低或高)且一直大于等于0,使得开关管电路对噪声不灵敏。

图4 开关电容阵列

图5 MOS开关管

2.4 缓冲电路

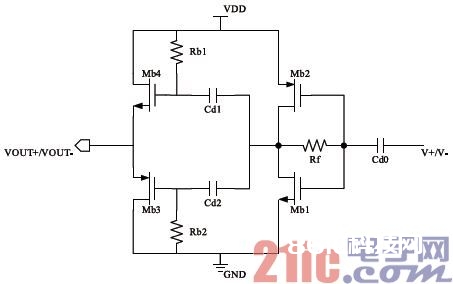

图6所示为缓冲电路,由一个反相器和一个推挽扩大器组成,选用两级电路之后具有高阻隔度。其间Rb1和Rb2是偏置电阻;Rf是反应电阻,可使电路更安稳;Cd0、Cd1和Cd2是隔直电阻,使各电路的偏置彼此独立,互不影响。

图6 缓冲电路

3.仿真成果

3.1 作业电流

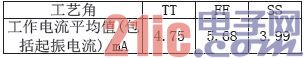

图7所示为仿真得到的作业电流,平均值为4.75mA,假如除掉起振时分的过冲电流的话,根本上可以到达4mA。表2对各个工艺角下的作业电流做了比照,可以看出作业电流最坏状况下为5mA左右,功耗契合规划要求。

表1 操控字0111下的作业电流

图7 作业电流(0111 TT)

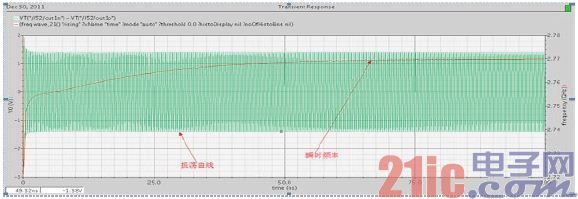

3.2 瞬态特性

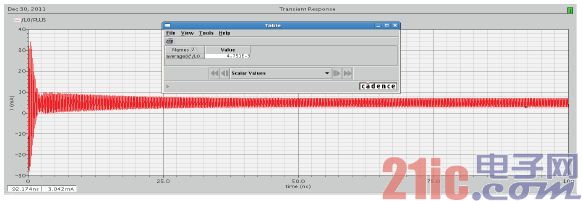

图8所示为瞬态仿真的成果。在开始条件中设置一个500mV的电压之后,VCO可以快速起振,振动曲线和振动频率正常,完成VCO的根本功能。其它工艺角下成果相似。

图8 瞬态仿真成果(操控字为0111 vcon=0.9V,TT)

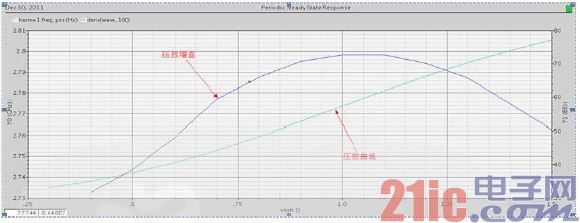

图9 压控特性曲线(TT)

图10 相位噪声曲线(操控字0000,vcon=0.9,TT)

3.3 压控特性曲线

图9所示为TT工艺角下的压控特性曲围为2.5G~3.1G,在完成宽调谐规模的一起又坚持了较低的压控增益。操控字为1110时压控增益较低,平均值为60MHz/V左右。其它工艺角下成果相似。

3.4 相位噪声

图10为在0000操控字下仿真得到的相位噪声曲线,对不同工艺脚剖析相位噪声,可看出相位噪声跟着操控字的添加而减小,因而在对TT工艺角的一切操控字进行相位噪声仿真之后,只需对FF和SS工艺角的第一个操控字和最终一个操控字以及中心的一部分操控字的相位噪声进行仿真,便可知一切操控字下的相位噪声功能。在频偏为1MHz时相位噪声根本散布在-118dBc/Hz~-122dBc/Hz,根本满意低相位噪声的要求。

4.结语

本文规划了可运用于DRM/DAB接纳机的压控振动器,并对一般的电路结构进行改善,以降低功耗和相位噪声,经仿真剖析,功能满意规划要求,但仍有些需求改善的当地,在后续规划中应经过进一步优化可变%&&&&&%的偏置电压及改善算法,进步压控增益曲线的线性度及相位噪声曲线的滑润性。