上下电时序方案:

1PMIC(DAS9061/DA9080)

2GPARK(SLG46582)

3GPARK(SLG46582)

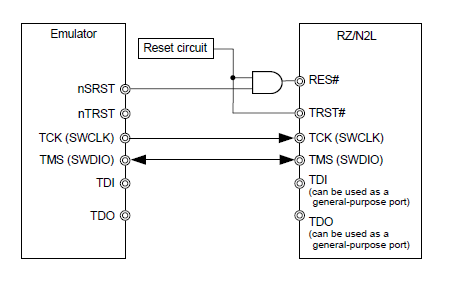

二复位电路

RES复位除了仿真电路以外的LSI外设,所以仿真器的复位需要连到此信号。

TRST复位TAP(Test Access Port),仿真器复位管脚不能连到此处,否则不能仿真,不用此管脚时,可通过一个下拉电阻接地,或和RES接相同的信号,注意不能悬空。

仿真器端有2个复位信号:

nSRST系统复位,一定要接,可通过调试器复位系统,方便调试。

nTRSTTAP复位,可不接。

接线图参考如下:

三并口

只用一个SDRAM时,只能用CS3,CS2不能单独用。

ECAT:推荐使用MII接口,小地址IN,大地址OUT,址需要连续,地址0一般不用。

1YT8512注意

LED1、PHYAD[1]、ETHn_LINK,3个信号在同一个管脚复用,所以需要做以下操作:

①LED的状态需要保持在稳定状态,即不能做成闪烁状态。

PHY寄存器改成0x30,收发包时,LED亮,down时,LED灭

LEDO对应的寄存器为ext Reg0x40C0;(上电默认值为0x0311)

LED1对应的寄存器为ext Reg0x40C2;(上电默认值为0x0320)

向这两个寄存器赋不同值,则LED做相应的状态显示,典型几种配置如下:

ext Reg0x40C0/0x40C3 配置值

动作行为

0x0311

link在10M时,LED亮;link在10M且收发包,LED闪

0x0320

link在100M时,LED亮;link在100M且收发包,LED闪

0x30

link或收发包时,LED亮;link down时灭

0x1300

收发包时闪烁;不收发包即灭

②YT8512的LED内部有自动检测外部上下拉状态的判断LED有效的功能,要对应判断MPU的link的极性,否则网络会反复link-up,link-down。

PHY的PHYAD[1]地址如果为1,则LED1外部为上拉,LED1信号为低时,灯亮。此时需要配置MPU的link检测状态的极性PHYLNK.CATLNK为低,即检测到低电平,判断为link,LED亮。

PHY的PHYAD[1]地址如果为0,则LED1外部为下拉,LED1信号为高时,灯亮。此时需要配置MPU的link检测状态的极性PHYLNK.CATLNK为高,即检测到高电平,判断为link,LED亮。

YT8512有两个LED管脚输出,分别是pin24-LED0,pin24-LED1。两管脚内部都有弱下拉电阻。

除了当作LED输出管脚外,它们在Power on Strapping阶段,还当作PHY地址配置管脚用,所以有时这两个管脚外部会有强上拉或强下拉(4.7k)。

LED管脚输出极性(即高有效还是低有效)与其管脚上所接的上拉电阻还是下拉电阻有关。(有外部上下拉电阻,则以外部为准,无外部上下拉电阻,则依赖内部默认上下拉电阻)

有上拉电阻,则为低有效(即需要外界LED灯的阴极);有下拉电阻,则为高有效(外界LED灯的阳极)

a 上拉、sink模式

b 下拉、source模式

①PHY和RJ45连接器之间的变压器是必须的,有些RJ45集成了变压器的功能,可以简化电路

②从MAC接收参考时钟或输出参考时钟到MAC,如果将参考时钟输出到MAC,25MHz晶体/时钟源应连接到PHY

③发射机时钟频率的总偏差由IEEE 802.3u规定为±100PPM(首选为±50PPM)

④检查MDIO是否需要一个外部上拉电阻

⑤考虑在信号源附近增加串联终端电阻以减少信号线上的反射

3PCB走线

①RMII/MII的阻抗为50欧姆±10%,大多数布线的正常标准。

②所有MII/RMII信号线(数据线、时钟线和其他)在单层上布线,并具有精确的长度匹

数据线和时钟线的迹长偏差应在10mm以内

应避免通孔

③MII/RMII信号的路径应该尽可能的直,且越短越好。否则,轨迹弯曲不应超过45度。

④时钟信号走线硬尽可能短,特殊情况需要较长布线时,要可被地线屏蔽。

⑤在信号层下面或上面放置一个地面层,以便MII/RMII信号的返回电流随时返回

五DSMIF

由于MPU是master,CLK信号是master发送,DATA是从器件反馈回来。如果走线过长,一来一回,此时回来的DATA和MPU发送的CLK相比,可能会有相位差,导致数据错位,所以常规做法是通过另外一根的时钟信号线拿过来时钟信号。

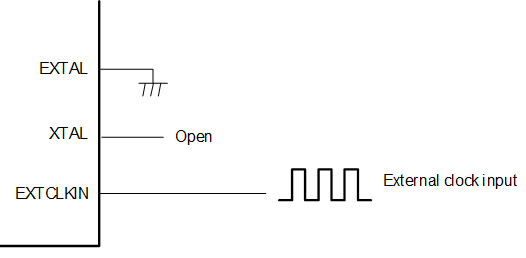

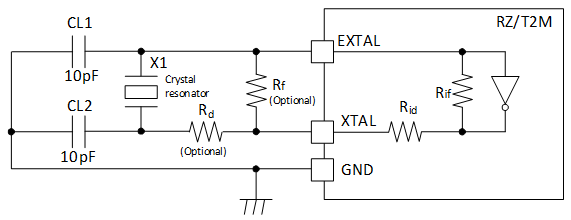

六始终

1尽量使用有源晶振,EXTAL连接到VSS,XTAL保持开路。

2使用无源晶振,晶振和电容尽可能靠近EXTAL和XTAL引脚,晶体的PCB周围最好用GND包起来,用于屏蔽的GND走线宽度应不小于0.3 mm,与相邻走线之间应保持0.3 mm ~ 2.0 mm的距离。

七MDV管脚

MDV0~MDV2对应ETH0~ETH2,根据实际的PHY芯片选择对应的1.8V还是3.3V。

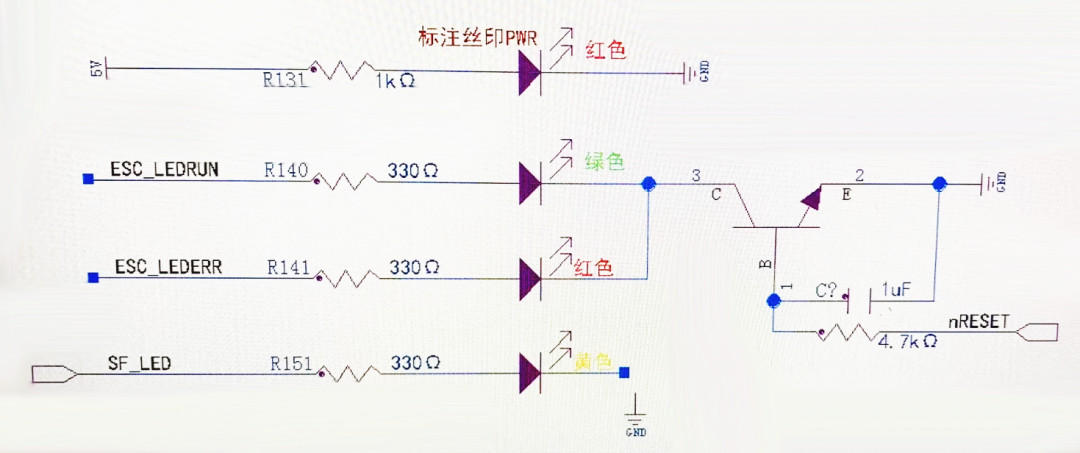

MDV1和ESC_LEDRUN,MDV2和ESC_LEDERR管脚复用:

如果MDV需要接到上拉,不做特殊处理的话,上电瞬间ESC模块没起来的时候,LEDRUN和LEDERR可能会亮,直到ESC模块控制此2个管脚,则可按正常状态点亮,为避免此种情况,可以按以下硬件方式处理。

MDV3~MDV4对应XSPI0,XSPI1,根据外部配置的存储芯片类型确定。

MDD管脚为常低电平。