导言

图画增强最早起源于人类的空间探究计划。从卫星或飞船上取得的关于地球和太阳系中行星的图画因为多种原因而降质,这些原因如成像设备受运用环境的束缚,相机和方针的相对运动,相机机械振荡,飞行器的跳动和翻转等等,获取图画的价值非常贵重,图画的降质形成科学含义上的丢失也是巨大的。因而由降质图画取得清楚图画的尽力对错常有含义的。图画增强技能是经过采纳恰当的增强处理使本来模糊不清乃至底子无法分辩的原始图片处理成清楚、清楚的富含很多有用信息的可用图画。因而,增强处理技能在医学、遥感、微生物、以及军事等范畴得到了广泛使用。

图画增强一般选用软件或硬件处理的办法。软件处理首要经过核算机来完结杂乱、高精度的图画处理算法,这种办法具有灵敏、便利、精度高级长处;可是选用软件处理的办法速度上会受限,在对体系实时性要求高的场合往往不能满意要求,比方航天或微波遥感范畴,需求实时观测处理信息,及时宣布相应的操控指令,这种条件下,软件处理是无法满意要求的。因为软件处理的这种局限性,选用高速的DSP或FPGA来完结实时图画处理显得尤为火急。DSP是专用的信号处理芯片,它内部硬件集成了许多专为信号处理而规划的部件,比方ADI公司的TigerSHARC系列芯片,它的内部有位反序部件,很简单完结FFT(快速傅立叶改换),因而,DSP被广泛使用于图画处理范畴。可是,因为技能壁垒的原因,航天范畴很难

得到航天等级的芯片,因而在一些要害的使用体系中,咱们则选用FPGA来完结实时图画处理。一起,FPGA以其高的处理速度、灵敏的操控及接口才能,广泛使用于实时图画处理范畴。现在的FPGA芯片一般都集成了DSP内核,这对图画处理带来了便利。针对这种状况,本文提出一种依据FPGA完结的SOPC,用于完结图画的增强处理。

1、像对比度增强算法原理

图画增强的办法一般分为两类:空间域和频域。本文则选用了空间域的办法。空间域办法首要使用某一原则来完结图画灰度值映射,然后调整图画灰度的动态规模,从而完结图画对比度增强。这种办法能够描绘为:

2、规划思路

在实际状况中,咱们关怀的是图画的方针,对布景不太重视。由式(1)可知,在空间域中,图画对比度增强处理能够理解为依照某一原则对图画像素点灰度值进行映射。依照式(2),选用分段灰度改变,对方针和布景别离选用不同的改换原则,对图画中的不同灰度信息进行灵敏处理。

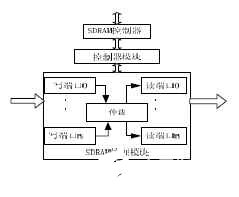

规划选用了PCI总线以32位传送数据,速度较快,PCI桥接芯片用于衔接PCI总线与板级部分总线。SOPC内部逻辑模块之间的衔接关系由Avalon总线树立。在板级部分总线与Avalon总线之间树立通讯模块,使主机能够经过PCI总线、板级部分总线和Avalon总线对SOPC组件进行拜访与操控。SDRAM用于存储处理前、后的图画数据。图画处理模块在有处理数据的使命或现已处理完毕时,与SDRAM办理与操控器进行交涉,获取SDRAM中的数据或把数据存入SDRAM。

3、体系结构及其功用完结

图1体系结构

3.1通讯模块

通讯模块担任板级部分总线与FPGA内部总线桥之间的通讯。因为SOPC内部各模块之间的逻辑衔接由FPGA内部总线桥完结,因而通讯模块的树立能够答应用户从主机经过PCI总线和板级部分总线拜访SOPC组件。该模块作为FPGA内部总线桥的一个主控接口,对总线桥上的其他从外设进行拜访和操控。

3.2 SDRAM(同步动态存储器)办理与操控器模块

该模块的作业时钟独立于体系时钟,包含三部分规划如图2所示:SDRAM办理模块、操控器模块与SDRAM操控器。(1)SDRAM办理模块担任对存储图画数据的SDRAM存储空间做合理的分配,使待处理数据与处理后的数据别离放置在不同的存储单元,它作为FPGA内部总线桥流形式从外设,读写端口的数量可装备,这些读写端口能够以流传输形式把图画数据读出或写入SDRAM。(2)操控器模块作为FPGA内部总线桥的主控接口,担任SDRAM办理模块与SDRAM操控器之间的衔接,并和谐两者之间的拜访。(3)SDRAM操控器担任对SDRAM的操控。

图2 SDRAM办理与操控器模块

3.3 图画对比度增强算法模块

常用的并行处理有两种最基本的衔接形式:流水线衔接和并行阵列衔接。针对该算法,咱们选用流水线衔接,如图3 所示。在流水线结构中, 一个大使命被分解成杂乱性大致相同的小使命, 各小使命在流水线上一起履行, 整个使命的速度取决于履行时刻最长的子使命的履行时刻。因而, 具有处理速度高的特色。在一个时钟触发信号到来时,进程1对图画数据进行存储,一起,进程2对图画数据进行处理;下一个时钟触发信号到来时,进程1存储的数据送入进程2进行处理,一起,进程1存储下一个输入数据。这样就完结了流水线操作,并可确保在一个时钟周期内完结一个像素点的核算。

图3 流水线结构

因为该算法逻辑模块是使用SOPC技能,能够在软件开发东西SOPC Builder中作为自定制模块调用,因而,需设置两个寄存器:帧有用计数寄存器和行有用计数寄存器,它们依据FPGA内部总线地址的不同,一起作为FPGA内部总线的读或写寄存器,然后使自界说模块能够和FPGA内部总线进行通讯。依据算法需求,选用VHDL言语对算法逻辑建模,并以FPGA内部总线从外设的办法在SOPC Builder 中调用。

4、图画增强处理体系的完结及测验成果

考虑到规划优化的便利性,本规划选用标准化硬件描绘言语VHDL树立FPGA模块完结。对体系需求进行功用模块区分,依照自顶向下的规划办法生成各规划阶级,将规划使命分解为不同的功用元件,每个元件具有专门界说的输入输出端口并履行各自的逻辑功用。该SOPC规划经过以下过程完结:

(1) 依照体系需求,选用Top-Down的办法进行部件区分。

(2) 各部件依据功用要求选用VHDL进行模块树立,并仿真归纳优化。

(3) 使用SOPC Builder东西编译生成用户自定制模块。

(4) 调用已树立的IP模块并设置参数,装备生成片上体系。

(5) 在顶层VHDL文件中调用模块并示例化,进行信号衔接。

(6) 对整个体系进行管脚等束缚设置,全编译并进行行为和时序验证。

(7) 下载和硬件调试完结。

这儿咱们选用嵌入式逻辑分析仪Signal Tap II对规划中算法模块的信号节点进行测验,成果如图 4所示。

图 4测验成果

输入的图画数据宽度是8位。其间, iDVAL与iLVAL别离是图画处理算法模块的输入数据有用信号与行有用信号,由oDVAL与oLVAL驱动;iDATA与oDATA别离是原图画数据与处理后数据,在iDVAL与iLVAL一起置’1’时,原图画数据被读入图画处理模块进行处理。

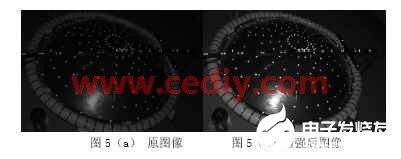

5、试验成果及定论

该规划对一幅巨细为3008*2000的图画进行处理试验,图画增强前后如图5(a)、图5(b)所示。很显着,图5(b)在增强方针对比度的一起限制了布景,取得了很好的增强作用。这一点也能够从式(3)来判别,两幅图画的对比度函数值别离为37dB和43dB,在本体系处理后的图画对比度增强了5dB。在SOPC体系时钟为50MHz时,每一帧的处理时刻为

![]()

而在PenTIum 4、CPU 3GHz、256MB内存的PC上经过Matlab用代码完结则需0.9850s。该规划选用FPGA完结图画实时处理,与使用软件处理图画的办法比较起来,有显着的速度优势。依据FPGA规划办法灵敏完结图画的实时处理,是往后图画处理开展的一个方向,尤其是在大数据量处理和高速实时处理要求较高的场合。

本文作者立异点:提出了一种依据FPGA的SOPC,该SOPC快速完结图画增强处理,满意实时图画处理的要求;一起,体系构成灵敏,可依据图画增强处理算法需求,对规划中模块的可重复开发。

责任编辑:gt