作者 耿新林 田怡博 段誉(电子科技大学 电子科学与工程学院,四川 成都 611731)

摘要:本文根据TSMC 65

nm工艺规划出了一个高频宽带PLL,其间VCO模块选用双VCO架构、鉴频鉴相模块选用三态鉴频鉴相器与电荷泵架构、环路滤波器选用二阶低通无源滤波器、分频器模块选用整数N型架构。整个锁相环 输出信号分辨率为100

输出信号分辨率为100

MHz,作业规模掩盖26 GHz -41 GHz,且在28 GHz相位噪声为 -124.2 dBc/Hz@10 MHz。

关键词:锁相环 ;宽带;高频

;宽带;高频

*曾获第二届(2018)全国大学生集成电路立异创业大赛决赛三等奖。

0 导言

本规划是2018年全国大学生集成电路立异创业大赛IEEE杯工程之星的处理方案,本题意图中心要求是规划一个频率调谐规模掩盖5G基站间毫米波通讯(28

GHz -39 GHz)的PLL,以尽或许小的相位噪声为主要性能目标,要求输出分辨率为100

MHz。为了到达中心要求,咱们选用了电荷泵整数N型PLL,其间VCO模块选用双VCO架构,鉴频鉴相模块选用均由NMOS作为开关管的电荷泵结构,除法器模块选用嵌入逻辑门的RLTSPC触发器的2/3分频器的电路结构。

1 PLL全体规划

VCO模块运用双VCO结构,并选用操控VCO交叉耦合对偏置的办法挑选作业的VCO,避免了不同VCO彼此串扰带来的相位噪声恶化。并运用差分的shunt

peak结构Buffer,极大进步了VCO的带负载才能。鉴频鉴相模块选用了经过添加延时模块的方法减小死区,并选用均由NMOS作为开关管的电荷泵结构,极大按捺了电荷泵非抱负效应。经过调整环路滤波器的参数,在理论上取得挨近60°的相位裕度。在除法器模块中,经过调整传统2/3分频器的电路结构、运用嵌入逻辑门的RLTSPC触发器,进步了除法器全体的作业速度。并经过将晶振输入频率2分频后,再输入到PFD作为参阅频率的方法,进步了PLL输出频率的分辨率。

2 VCO模块

为了完成26 GHz~41

GHz的频率掩盖规模VCO模块选用了双VCO架构,一起将双VCO的操控开关放在了VCO的尾电流源处,这样既能够下降一半功耗(PLL在作业时只要一个VCO发动),又能够彻底避免两个VCO之间的信号串扰,优化了相位噪声。

传统的VCO Buffer是运用电阻电容耦合的反相器。实践测出来该结构在40

G时速度不够快,无法正常作业。经过查阅文献,终究运用了文献[1]中说到的shunt

peak结构[1],并在此基础上改成了四输入差分结构,这样只需要一个差分电感即可完成榜首级Buffer。终究咱们选用了两级这样的结构,不只使VCO与除法器完成了较好的阻隔,一起也使VCO完成了轨到轨的输出。

假如将变容管直接接入谐振腔,在关怀的电压规模内(0 V~0.8

V),KVCO会有较大的非线性,这会导致PLL在较高的电压处无法确定。因而为了确保PLL的掩盖规模,必需要优化KVCO的非线性。经过调研挑选了文献[2]说到的偏置方法[2]。将两对变容管偏置在不同的电压下,以优化变容管的非线性。实践上,因为VCO掩盖的频率规模较大,而且选用4

bit的电容阵列(共16便条带),导致跟着频率的升高,每便条带的KVCO不断增大,这又带来了PLL高频或许失锁的问题,为了处理这个问题,下一步咱们考虑补偿高频子带的KVCO值,使他的改变尽量减小。

3 PFD、CP、LF模块

鉴频鉴相器(Phase Frequency Detecter)、电荷泵(Charge Pump)、环路低通滤波器(Loop

Filter)是锁相环 体系的重要组成部分。鉴频鉴相器存在死区问题;电荷泵存在种种非抱负效应;环路滤波器决议体系的环路特性,其间最困难的部分就是在相位裕度,带宽和相位噪声之间进行权衡。

体系的重要组成部分。鉴频鉴相器存在死区问题;电荷泵存在种种非抱负效应;环路滤波器决议体系的环路特性,其间最困难的部分就是在相位裕度,带宽和相位噪声之间进行权衡。

本规划PFD模块选用三态鉴频鉴相器,为处理鉴频鉴相器的死区问题,在其反应处参加两级恰当尺度的反相器进行延时,为电荷泵供给满意敞开时刻,减小死区。

传统电荷泵电路存在各种非抱负效应比方电荷同享效应。本规划选用一种均由NMOS操控电荷泵开断的结构[3]。这种电荷泵电路最大长处是它能够彻底去除电荷同享效应的影响,此外其结构简略且高度对称;一起因为没有选用运放的结构,其功耗较低。

环路滤波器选用二阶无源低通滤波器。因本规划的要点优化目标之一是相位噪声,而有源滤波器会引进新的噪声,故本规划选用无源滤波器。又因一阶滤波器不能很好滤去纹波,故本规划选用二阶滤波器。经matlab仿真,该PLL体系最佳相位裕度是56.4°,此刻对应带宽为0.211

MHz。

4 除法器

经过前期文献调研,咱们了解到现在干流的除法器结构有两种:吞脉冲除法器和除法链(Divider

Chain)结构。但因为吞脉冲除法器结构缺少模块化规划,故其规划缺少灵敏性且不利于地图,且其间的双模预分频计数器包括过多的逻辑门电路,导致其作业速度在TSMC65

nm CMOS工艺下仅能到达17

GHz,难以满意规划要求。相反,除法链结构由若干独立模块组成,可灵敏地对每一个模块进行独登时调整优化,特别是榜首级2/3分频器,其作业于电路的最高速度,需要对其进行特别的规划与优化。故本次规划中,选用多级2/3分频器级联的结构进行规划[4]。

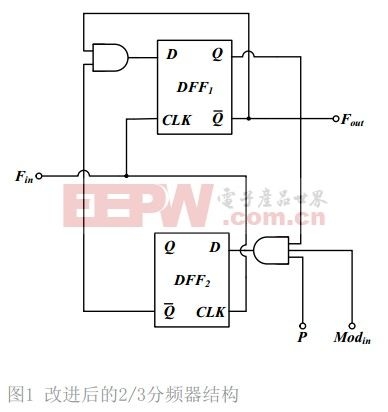

传统的2/3分频器[5]中包括了4个D锁存器和3个与门。因为时序逻辑电路规划中,级联逻辑器材越多,其作业速度越慢,故传统2/3除法器难以满意本规划要求。所以,本次规划中对传统2/3除法器的结构进行了改善,改善后的2/3分频器结构如图1所示。改善后的结构经过减少了与门的数量,并将两个不同触发沿的D锁存器合并为一个D触发器,大大减少了电路结构中的逻辑器材数量,减少了信号路劲的延时,进步了2/3分频器的作业速度。

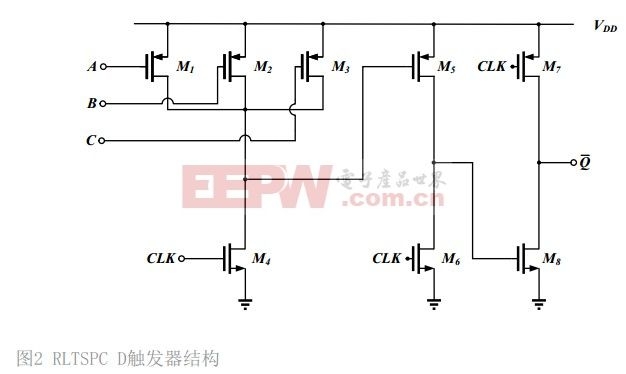

为了进一步的进步2/3锁存器的作业速度,本文提出了一种将2输入、3输入与门嵌入进D触发器并对其运用有比逻辑的RLTSPC

D触发器结构,如图2所示。

以上的优化调整,极大地进步了2/3分频器除法链的作业速度,使其能在TSMC 65 nm的工艺条件下,到达47

GHz的最高作业速度,并对输入进行256~510的接连可调的整数分频。

5 地图与全体仿真

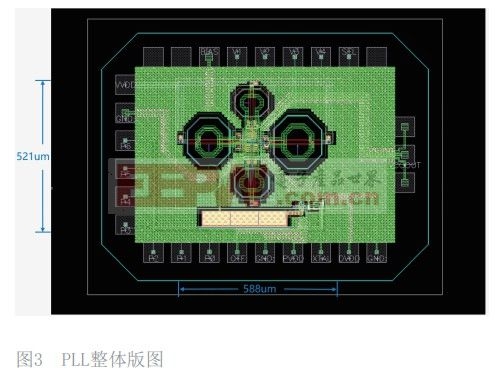

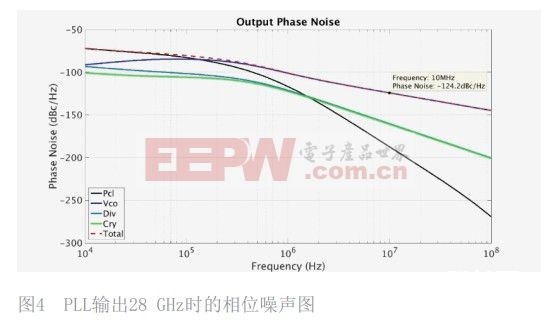

图3为PLL全体地图,地图面积约为0.31 mm2。图4为PLL输出28 GHz信号的相位噪声图。仿真结果表明所规划的PLL在输出28

GHz的信号时相位噪声为-124.2 dBc/Hz@10 MHz。图5为PLL别离输出26 GHz,28 GHz以及41

GHz信号时,VCO操控电压的改变图。仿真结果表明,VCO操控电压上的ripple均为1 mV左右,在5 μs时现已根本确定。

6 定论

本文根据TSMC 65 nm工艺规划出了一个在1 V电源电压下作业,输入参阅频率为100 MHz,作业规模掩盖26 GHz-41

GHz高频宽带PLL,整个锁相环 输出信号分辨率为100 MHz,确定时刻大约5 μs,功耗为44 mW,且在28 GHz相位噪声为 -124.2

输出信号分辨率为100 MHz,确定时刻大约5 μs,功耗为44 mW,且在28 GHz相位噪声为 -124.2

dBc/Hz@10 MHz。

参阅文献

[1]Chen Feng, Xiao Peng Yu, Wei Meng Lim, et al.A 40 GHz 65 nm CMOS

Phase-Locked Loop With Optimized Shunt-Peaked Buffer.IEEE MICROWAVE AND WIRELESS

COMPONENTS LETTERS, VOL.25, NO.1, 2015.

[2]Li S,You F.Optimal Design of a Wideband 10GHz LC-VCO with Small KVCO

Variation in 0.13m GSMC CMOS Process.IEEE International Conference on

Electronics Technology, 2018.

[3]Chang C R, Kuo L C.A New Low-Voltage Charge Pump Circuit for PLL.IEEE

International Symposium on Circuits and Systems, May 28-31, 2000.

[4]Yang Y C,Yu S A,Wang T, et al. A Dual-Mode Truly Modular Programmable

Fractional Divider Based on a 1/1.5 Divider Cell. IEEE Microwave and Wireless

Components Letters, 2005(15):754-756.

[5]Razavi B. A Family of Low-Power Truly Modular Programmable Dividers in

Standard 0.35 m CMOS Technology[M].Wiley-IEEE Press eBook Chapters,2003.

作者简介:

耿新林(1996-)男,硕士,研讨方向:射频、微波、毫米波、太赫兹集成电路。

段誉(1997-),男,本科生,研讨方向:射频、微波集成电路。

本文来源于科技期刊《电子产品世界》2019年第2期第81页,欢迎您写论文时引证,并注明出处