摘要:提出一种高频时钟电路的规划方案。运用一款先进的可编程时钟组成器MPC92433,依据FPGA的操控,完成4对LVDS信号输出。体系通过测验,输出时钟信号频率抵达1 GHz,能够广泛应用到各种数字电路规划中。

要害词:MPC92433;高频时钟;I2C;FPGA

时钟信号是任何数字电路规划的根底,而时钟源是雷达、通讯、测验仪器等电子体系完成高性能目标的要害,许多电子设备和体系功用的完成都直接依赖于高性能的时钟源。文中挑选时钟组成器MPC92433+FPGA的方法规划高频时钟源,完成了4路LVDS(Low Voltage Differen tial Sighals)电平信号输出。

MPC92433是一款高性能时钟组成源,它是3.3 V兼容、PLL针对性的时钟组成器,输出LVPECL电平规范差分信号的频率规模为42.50~1 468 MHz,最大时钟颤动为10 ps/1 GHz,一起具有芯片体积小、功耗低一级长处,因而能够很容易地完成高频时钟信号的组成。

FPGA挑选Xilinx公司的Spartan系列中的XC2S200E芯片,它能够供给最多15 552个逻辑单元,最多抵达600 000个系列逻辑门,具有分布式的RAM和BLOCKRAM,最多可达514个I/O,支撑19种规范,其间还包含LVDS、HSTL、PCI等功用,体系时钟频率达200 MHz,能够极大地满意规划的要求。

1 MPC92433介绍

1.1 首要性能特色

两路差分LVPECL兼容的高频率输出;输出频率通过2-wireI2C总线或并行接口编程;LVCMOS兼容的参阅时钟输入;两路LVCMOS兼容操控输入;两路输出同步时钟中止功用;彻底集成PLL。

1.2 结构阐明

MPc92433逻辑结构如图1所示。外部晶体作为芯片内部晶振的频率基准,一个LMCOMS兼容的时钟信号用来作为PLL参阅信号。内部晶体振荡器被分频后与PLL相乘,VCO(航向操控振荡器)内部PLL动态规模为1 360~2 850 MHz,其输出通过I2C(Inter Integrated Circuit)或并口装备。晶体振荡器频率fXTAL、PLL预分频器P、反应分频器M和PLL后分频器N一起决议输出频率。PLL反应通道是内部的,分频器N通过I2C或并口装备可供给7种份额装备(2,4,6,8,12,16,32),一起它具有扩展性,可供给50 Ω占空比。高频输出端QA和QB输出差分信号,而且QB能够装备为运转在任何1x或1/2x的时钟频率或OA输出。

芯片有串行和并行两种装备接口。并行接口的意图是直接通过硬件装备PLL没有分隔的引脚,可是它不支撑对PLL的读操作,而串行接口是一个I2C形式接口,答应进行读/写操作。在本规划中,选用串行接口形式,寄存器读/写操作通过芯片的数据装备接口SDA和时钟装备接口SCL完成,芯片作业在主从形式下。

2 串行IC接口形式

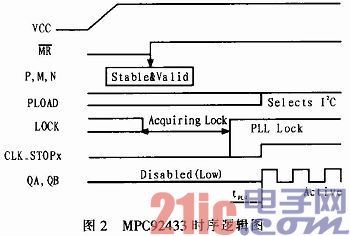

MPC92433的时序逻辑如图2所示。

当对MPC92433加电后,其他并行接口管脚M[9:0]、NA[2:0]和P都是开路状况。当 处于上升沿时,PLL开端默许的装备,这种初始装备能够在任何时候通过串行接口被从头编程操控。

处于上升沿时,PLL开端默许的装备,这种初始装备能够在任何时候通过串行接口被从头编程操控。

3 硬件电路规划

3.1 规划原理

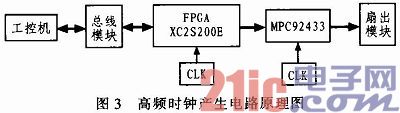

FPGA通过E2PROM加载操控程序后,MPC92433依据写入的程序对相应管脚进行逻辑装备,输出所需求的时钟信号。因为MPC92433输出的是两路差分LVPECL电平信号,通过扇出模块差分出4对LVDS(Low Voltage DifferentialSignals)电平信号。电路原理框图如图3所示。

电路首要包含4部分:FPGA模块、时钟模块、扇出模块和总线模块。FPGA模块首要完成程序及相关参数加载功用;时钟模块通过对时钟芯片的装备完成高频时钟的生成;扇出模块完成差分信号由1路LVPECL电平信号扇出4路LVDS信号的功用;总线模块完成对电路的读写功用。

3.2 电路规划

要得到高频时钟信号,首要是完成FPGA对时钟芯片的操控,即通过FPGA的I/O接口完成对MPC92433芯片的管脚逻辑界说。MPC92433芯片首要功用引脚 、NA、NB等别离与FPGA衔接,接口形式为形式。

、NA、NB等别离与FPGA衔接,接口形式为形式。

FPGA加载成功后,操控MPC92433芯片输出高频时钟信号,差分信号通过双芯LEMO传输到扇出电路构成1:4的LVDS信号。输出的LVDS信号抵达接纳端时,一般要求接纳端具有很高的阻抗。在终端匹配大电阻能够使电流大部分流过电阻,当输入信号翻转时,改动通过电阻的电流方向,能够完成逻辑“0”和“1”的状况交换。为了提高抗噪声作用,差分信号之间用75 Ω电阻串联。

4 结束语

体系通过测验,能够满意输出1 GHz的高频时钟信号,一起因为MPC92433是可程控的,因而能够在原有电路上进行改善,使得电路输出更高频率的时钟信号。

电路中差分的电平信号是LVDS和LVPEL两种,要满意信号完整性和较强的抗搅扰才能,除了要使负载和信号线的阻抗相匹配之外,在规划中还要尽量防止阻抗不匹配的环节呈现,关于差分信号线还应该留意以下几点:1)差分线脱离器材引脚后,要尽彼此接近,以保证耦合到信号线的噪声为共模噪声:2)信号线的长度应该匹配,否则会引起信号歪曲和电磁搅扰:3)不能够只是依托软件的主动布线功用,要依据实际情况细心修正差分线的阻抗匹配和阻隔;4)尽量削减过孔的运用,防止其他一些引起阻抗不接连的要素;5)信号线在不同的信号层时,要留意调整差分线的宽度和距离,防止因介质改动引起的阻抗不接连。