数据总线是飞机航电体系中首要运用的数字电子设备之一,其典型代表是飞机内部时分制指令/呼应式多路传输数据总线MIL-STD-1553B。它使用一条屏蔽的双绞线进行带有时钟信息的数据传输。高可靠性1553B已成为我国航空航天范畴广泛选用的军用总线规范。因为1553B总线协议控制器根本依赖于进口的专用器材,价格昂贵,还受到约束,而且这些器材需求外围的硬件电路合作作业,假如完结整个总线接口板的规划,还需求独自的MCU,集成度不高,这样就在某种程度上约束了规划能力。跟着嵌入式技能的开展,可编程片上体系规划 SoPC技能已广泛应用于许多范畴。这儿选用SoPC技能,以Virtex-II Pro FPGA为中心,完成1553B航空总线传输协议的接口逻辑规划。

1553B航空总线传输协议规范

现在广泛选用的1553B规范是依据1973 年军标1553原版基础上开展。1553B是一种集中控制式、飞机内部时分指令/呼应型多路串行数据总线规范。具有高可靠性和灵敏性。已经成为现代航空机载体系设备互联的要害技能。广泛应用于飞机、舰船等兵器渠道。1553B数据总线的传输速率为1Mb/s,协议规则3种字:命令字、数据字和状态字。字的长度为20 bit,且由同步头(3 bit)音讯块(16 bit)和奇偶位(1 bit)3部分组成。信息量最大长度为32。总线体系由一个总线控制器(BC)与不多于31个的长途终端(RT)组成,有时体系中还可参加总线监控器 (MT)。总线上传输的信息格局首要有BC到RT,RT到BC,RT到RT,以及播送办法和体系控制办法。

体系规划

该体系选用Xilinx公司的Virtex-II Pm XC2VP30 FPGA为中心,该器材内部带有2个PowerPC 405处理器核。总线接口协议完成是根据Xilinx Virtex-II Pro开发体系渠道,Virtex-II Pro开发渠道是整个体系的中心。这样能够快速建立1553B总线完成渠道。体系的硬件渠道首要由Vinex-II Pro开发板、总线转换器、总线终端设备和主控计算机构成,体系结构如图1所示。

在体系开发中,为了进步开发功率,一起体系首要验证的便是1553B总线协议模块,因而可充分使用Xilinx公司的Virtex-II Pro开发板。开发板上具有丰厚的资源,首要包含:XC2VP30器材、SDRAM (可扩展到2 GB)、高速SelectMAPFPGA装备PROM、RS232串口、嵌入渠道的USB装备端口、高速体系扩展接口(与FPGA的I/O引脚相连)并可挑选差分或单端形式、PS2接口、AC97音频接口、板上10/100 M以太网设备等等。这些丰厚的板上资源为1553B总线协议逻辑的开发供给支撑。

1553B总线协议开发首要在FPGA器材中开发,因而FPGA自身功用的好坏将影响体系的开发。XC2VP30内部具有2个PowerPC 405处理器核、13 969个Slices、分布式RAM为428 KB、136个乘法器单元、块RAM为2 448 KB、8个DCM、8个多吉比特收发器。因而,选用XC2VP30FPGA彻底满意1553B总线逻辑开发需求。

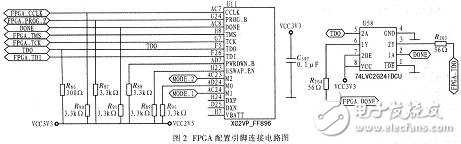

该体系规划选用Virtex-II Pro系列XC12VP30型FPGA,而FPGA的装备则是硬件规划中很要害的问题。FPGA装备是对其内容进行编程。选用SRAM工艺的FPGA,每次上电后都需重新装备。XC2VP30经过形式引脚挑选装备形式,其间M2、M1和M0是专用引脚,HSWAP_EN和装备形式引脚相组合,决议I/O引脚在装备过程中是否具有上拉功用。默许情况下,HSWAP_EN置为高电平,此刻在装备过程中封闭I/O引脚的上拉功用;当其置为低电平时,I/O引脚具有上拉功用。当挑选某些装备形式时,CCLK可作为FPGA的信号输出引脚,也可作为外部时钟的输入信号,这些引脚不受VCCO的影响,而是选用2.5 V的辅佐电源(VCCAUX)。

图2给出的是FPGA装备引脚衔接电路图。XC2VP30支撑5种装备形式,分别是 Slave-serial形式、Master-serial形式、Slave SelectMAP形式、MasterSelectMAP形式和Boundary-Scan (IEEE 1532/IEEE 1149)形式。经过调整装备引脚MO、M1、M2调整装备形式。该体系规划只供给两种装备形式,在XC2VP30的装备电路中将M0引脚拉为高电平,这样只能挑选MasterSelectMAP形式和Boundary-Scan形式(即鸿沟扫描形式)。Master SelectMAP形式是SelectMAP形式的主版别形式,在由XC2VP30所供给的CCLK信号的效果下,器材经过字节宽度数据总线即装备器材 XCF32P的[D7:D0],除了CCLK是由FPGA供给之外,装备时序与Slave SelectMAP形式类似。在鸿沟扫描形式下,XC2VP30经过专用装备引脚CCLK,DONE,PROG_B,TDI,TDO,MS,TCK依照 IEEE 1149.1规范进行装备。

选用根据SoPC的规划办法,完结了MIL-STD-1553B航空总线接口逻辑的开发,并使用仪器测验体系。将该体系规划的总线协议接口逻辑固化到 FPGA中。可替代国外进口的专用1553B总线控制器器材,然后脱节长时间依赖于国外进口器材的捆绑,具有杰出的军事和经济效益。该体系的立异之处是选用先进的SoPC技能开发FPGA,全面完成1553B总线接口逻辑,体系具有装备灵敏,易于扩展等特色。