关于电容退耦,许多材料中都有触及,可是论述的视点不同。有些是从部分电荷存储(即储能)的视点来阐明,有些是从电源分配体系的阻抗的视点来阐明,还有些材料的阐明更为紊乱,一会提储能,一会提阻抗,因而许多人在看材料的时分感到有些利诱。其实,这两种提法,本质上是相同的,只不过看待问题的视角不同罢了。为了让咱们有个清楚的知道,本文别离介绍一下这两种解说。

1、从储能的视点来阐明电容退耦原理。

在制造电路板时,一般会在负载芯片周围放置许多电容,这些电容就起到电源退耦作用。

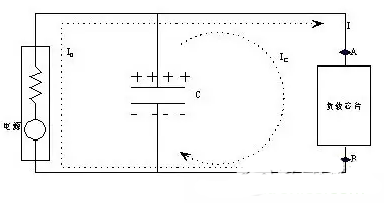

其原理可用图 1 阐明。

图 1 去耦电路

当负载电流不变时,其电流由稳压电源部分供给,即图中的 I0,方向如图所示。此刻电容两头电压与负载两头电压一起,电流 Ic 为 0,电容两头存储适当数量的电荷,其电荷数量和电容量有关。当负载瞬态电流发生改变时,因为负载芯片内部晶体管电平转化速度极快,有必要在极短的时间内为负载芯片供给满意的电流。可是稳压电源无法很快呼应负载电流的改变,因而,电流 I0 不会立刻满意负载瞬态电流要求,因而负载芯片电压会下降。可是因为电容电压与负载电压相同,因而电容两头存在电压改变。关于电容来说电压改变必定发生电流,此刻电容对负载放电,电流 Ic 不再为 0,为负载芯片供给电流。

只需电容量 C 满意大,只需很小的电压改变,电容就能够供给满意大的电流,满意负载瞬态电流的要求。这样就确保了负载芯片电压的改变在容许的规模内。这儿,适当于电容预先存储了一部分电能,在负载需求的时分释放出来,即电容是储能元件。储能电容的存在使负载耗费的能量得到快速弥补,因而确保了负载两头电压不至于有太大改变,此刻电容背负的是部分电源的人物。

从储能的视点来了解电源退耦,十分直观易懂,可是对电路规划协助不大。从阻抗的视点了解电容退耦,能让咱们规划电路时有章可循。实践上,在决议电源分配体系的去耦电容量的时分,用的便是阻抗的概念。

2、从阻抗的视点来了解退耦原理。

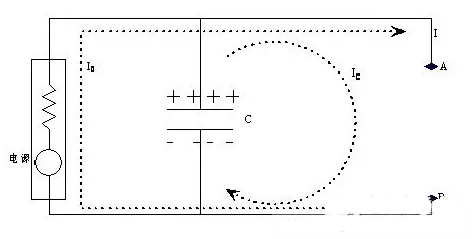

将图 1 中的负载芯片拿掉,如图 2 所示。从 AB 两点向左看过去,稳压电源以及%&&&&&%退耦体系一同,能够当作一个复合的电源体系。这个电源体系的特点是:不管 AB 两点间负载瞬态电流怎样改变,都能确保 AB 两点间的电压坚持稳定,即 AB 两点间电压改变很小。

图片 2 电源部分

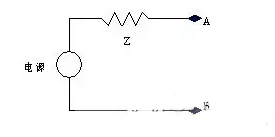

咱们能够用一个等效电源模型表明上面这个复合的电源体系,如图 3

图 3 等效电源

关于这个电路可写出如下等式:

(公式 2)

咱们的终究规划方针是,不管 AB 两点间负载瞬态电流怎样改变,都要坚持 AB 两点间电压改变规模很小,依据公式 2,这个要求等效于电源体系的阻抗 Z 要满意低。在图 2 中,咱们是经过去耦电容来抵达这一要求的,因而从等效的视点动身,能够说去耦电容下降了电源体系的阻抗。另一方面,从电路原理的视点来说,可得到相同定论。电容关于沟通信号出现低阻抗特性,因而参加电容,实践上也的确下降了电源体系的沟通阻抗。

从阻抗的视点了解电容退耦,能够给咱们规划电源分配体系带来极大的便利。实践上,电源分配体系规划的最底子的准则便是使阻抗最小。最有用的规划办法便是在这个准则指导下发生的。

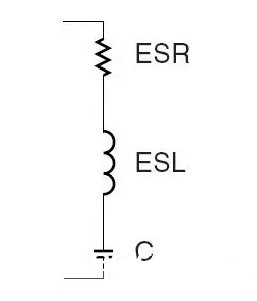

正确运用电容进行电源退耦,有必要了解实践电容的频率特性。抱负电容器在实践中是不存在的,这便是为什么常常听到“电容不仅仅是电容”的原因。

实践的电容器总会存在一些寄生参数,这些寄生参数在低频时体现不明显,可是高频状况下,其重要性可能会超越容值自身。图 4 是实践电容器的 SP%&&&&&%E 模型,图中,ESR 代表等效串联电阻,ESL 代表等效串联电感或寄生电感,C 为抱负%&&&&&%。

图 4 电容模型

等效串联电感(寄生电感)无法消除,只需存在引线,就会有寄生电感。这从磁场能量改变的视点能够很简单了解,电流发生改变时,磁场能量发生改变,可是不行能发生能量跃变,体现出电感特性。寄生电感会推迟电容电流的改变,电感越大,电容充放电阻抗就越大,反响时间就越长。等效串联电阻也不行消除的,很简单,因为制造电容的材料不是超导体。

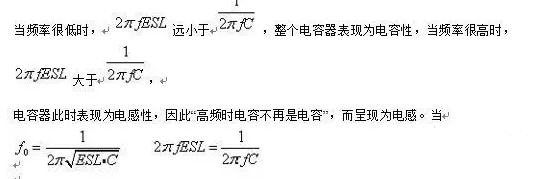

评论实践电容特性之前,首要介绍谐振的概念。关于图 4 的%&&&&&%模型,其复阻抗为:

(公式 3)

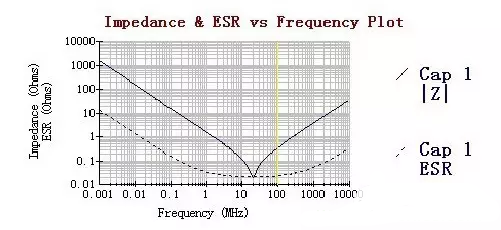

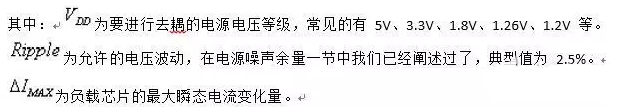

时,此刻容性阻抗矢量与理性阻抗之差为 0,电容的总阻抗最小,体现为纯电阻特性。该频率点便是电容的自谐振频率。自谐振频率点是区别电容是容性仍是理性的分界点,高于谐振频率时,“电容不再是电容”,因而退耦作用将下降。因而,实践电容器都有必定的作业频率规模,只要在其作业频率规模内,电容才具有很好的退耦作用,运用电容进行电源退耦时要特别重视这一点。寄生电感(等效串联电感)是电容器在高于自谐振频率点之撤退耦功用被消弱的底子原因。图 5 显现了一个实践的 0805 封装 0.1uF 陶瓷%&&&&&%,其阻抗随频率改变的曲线。

图 5 电容阻抗特性

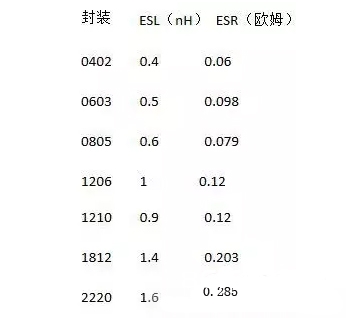

电容的自谐振频率值和它的电容值及等效串联电感值有关,运用时可查看器材手册,了解该项参数,确认电容的有用频率规模。下面列出了 AVX 出产的陶瓷%&&&&&%不同封装的各项参数值。

电容的等效串联电感和出产工艺和封装尺度有关,同一个厂家的同种封装尺度的电容,其等效串联电感根本相同。一般小封装的电容等效串联电感更低,宽体封装的电容比窄体封装的电容有更低的等效串联电感。

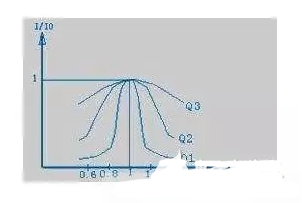

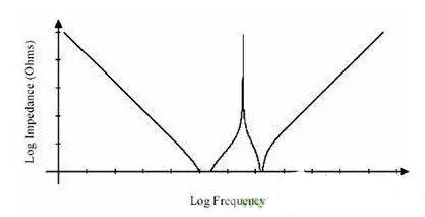

已然电容能够当作 RLC 串联电路,因而也会存在质量因数,即 Q 值,这也是在运用电容时的一个重要参数。

电路在谐振时容抗等于感抗,所以电容和电感上两头的电压有用值必定持平,电容上的电压有用值 UC=I*1/ωC=U/ωCR=QU,质量因数 Q=1/ωCR,这儿 I 是电路的总电流。电感上的电压有用值 UL=ωLI=ωL*U/R=QU,质量因数Q=ωL/R。因为:UC=UL 所以 Q=1/ωCR=ωL/R。电容上的电压与外加信号电压 U 之比 UC/U=(I*1/ωC)/RI=1/ωCR=Q。电感上的电压与外加信号电压 U 之比 UL/U=ωLI/RI=ωL/R=Q。从上面剖析可见,电路的质量因数越高,电感或%&&&&&%上的电压比外加电压越高。

图 6 Q 值的影响

Q 值影响电路的频率挑选性。当电路处于谐振频率时,有最大的电流,违背谐振频率时总电流减小。咱们用 I/I0 表明经过电容的电流与谐振电流的比值,即相对改变率。表明频率违背谐振频率程度。图 6 显现了 I/I0 与联系曲线。这儿有三条曲线,对应三个不同的 Q 值,其间有 Q1》Q2》Q3。从图中可看出当外加信号频率 ω 违背电路的谐振频率 ω0时,I/I0 均小于 1。Q 值越高在必定的频偏下电流下降得越快,其谐振曲线越尖利。也便是说电路的挑选性是由电路的质量要素 Q 所决议的,Q 值越高挑选性越好。

在电路板上会放置一些大的电容,一般是坦电容或电解电容。这类电容有很低的 ESL,可是 ESR 很高,因而 Q 值很低,具有很宽的有用频率规模,十分适合板级电源滤波。

当电容装置到电路板上后,还会引进额定的寄生参数,然后引起谐振频率的偏移。充沛了解电容的自谐振频率和装置谐振频率十分重要,在核算体系参数时,实践运用的是装置谐振频率,而不是自谐振频率,因为咱们重视的是电容装置到电路板上之后的体现。

电容在电路板上的装置一般包含一小段从焊盘拉出的引出线,两个或更多的过孔。咱们知道,不管引线仍是过孔都存在寄生电感。寄生电感是咱们首要重视的重要参数,因为它对电容的特性影响最大。电容装置后,能够对其周围一小片区域有用去耦,这触及到去耦半径问题,本文后边还要详细叙述。现在咱们调查这样一种状况,电容要对间隔它 2 厘米处的一点去耦,这时寄生电感包含哪几部分。首要,电容自身存在寄生电感。从电容抵达需求去耦区域的途径上包含焊盘、一小段引出线、过孔、2 厘米长的电源及地平面,这几个部分都存在寄生电感。相比较而言,过孔的寄生电感较大。能够用公式近似核算一个过孔的寄生电感有多大。 公式为

其间:L 是过孔的寄生电感,单位是 nH。h 为过孔的长度,和板厚有关,单位是英寸。d为过孔的直径,单位是英寸。下面就核算一个常见的过孔的寄生电感,看看有多大,以便有一个理性知道。设过孔的长度为 63mil(对应电路板的厚度 1.6 毫米,这一厚度的电路板很常见),过孔直径 8mil,依据上面公式得:

这一寄生电感比许多小封装电容自身的寄生电感要大,有必要考虑它的影响。过孔的直径越大,寄生电感越小。过孔长度越长,电感越大。下面咱们就以一个 0805 封装 0.01uF 电容为例,核算装置前后谐振频率的改变。参数如下:容值:C=0.01uF。电容自身等效串联电感:ESL=0.6 nH。装置后添加的寄生电感:Lmount=1.5nH。

电容的自谐振频率:

装置后的总寄生电感:0.6+1.5=2.1nH。留意,实践上装置一个电容至少要两个过孔,寄生电感是串联的,假如只用两个过孔,则过孔引进的寄生电感就有 3nH。可是在电容的每一端都并联几个过孔,能够有用减小总的寄生电感量,这和装置办法有关。

装置后的谐振频率为:

可见,装置后电容的谐振频率发生了很大的偏移,使得小电容的高频去耦特性被消弱。在进行电路参数规划时,应以这个装置后的谐振频率核算,因为这才是电容在电路板上的实践体现。

装置电感对电容的去耦特性发生很大影响,应尽量减小。实践上,怎样最大程度的减小装置后的寄生电感,是一个十分重要的问题。

从电源体系的视点进行去耦规划

先插一句题外话,许多人在看材料时会有这样的困惑,有的材料上说要对每个电源引脚加去耦电容,而另一些材料并不是依照每个电源引脚都加去偶电容来规划的,仅仅说在芯片周围放置多少电容,然后怎样放置,怎样打孔等等。那么究竟哪种说法及做法正确呢?我在刚触摸电路规划的时分也有这样的困惑。其实,两种办法都是正确的,只不过处理问题的视点不同。看过本文后,你就完全了解了。

上一节讲了对引脚去耦的办法,这一节就来讲讲另一种办法,从电源体系的视点进行去耦规划。该办法本着这样一个准则:在感兴趣的频率规模内,使整个电源分配体系阻抗最低。其办法依然是运用去耦电容。

电源去耦触及到许多问题:总的电容量多大才干满意要求?怎样确认这个值?挑选那些电容值?放多少个电容?选什么原料的电容?电容怎样装置到电路板上?%&&&&&%放置间隔有什么要求?下面别离介绍。

闻名的 Target Impedance(方针阻抗)

方针阻抗(Target Impedance)界说为:

(公式 4)

该界说可解说为:能满意负载最大瞬态电流供给,且电压改变不超越最大容许动摇规模的状况下,电源体系自身阻抗的最大值。超越这一阻抗值,电源动摇将超越容许规模。假如你对阻抗和电压动摇的联系不清楚的话,请回忆“电容退耦的两种解说”一节。

对方针阻抗有两点需求阐明:

1、方针阻抗是电源体系的瞬态阻抗,是对快速改变的电流体现出来的一种阻抗特性。

2、方针阻抗和必定宽度的频段有关。在感兴趣的整个频率规模内,电源阻抗都不能超越这个值。阻抗是电阻、电感和电容一起作用的成果,因而必定与频率有关。感兴趣的整个频率规模有多大?这和负载对瞬态电流的要求有关。望文生义,瞬态电流是指在极短时间内电源有必要供给的电流。假如把这个电流看做信号的话,适当于一个阶跃信号,具有很宽的频谱,这一频谱规模便是咱们感兴趣的频率规模。

假如暂时不了解上述两点,没联系,持续看完本文后边的部分,你就了解了。

需求多大的电容量

有两种办法确认所需的电容量。榜首种办法运用电源驱动的负载核算电容量。这种办法没有考虑 ESL 及 ESR 的影响,因而很不准确,可是对了解电容量的挑选有优点。第二种办法便是运用方针阻抗(Target Impedance)来核算总电容量,这是业界通用的办法,得到了广泛验证。你能够先用这种办法来核算,然后做部分微调,能抵达很好的作用,怎样进行部分微调,是一个更高档的论题。下面别离介绍两种办法。

办法一:运用电源驱动的负载核算电容量

设负载(容性)为 30pF,要在 2ns 内从 0V 驱动到 3.3V,瞬态电流为:

(公式 5)

假如共有 36 个这样的负载需求驱动,则瞬态电流为:36*49.5mA=1.782A。假定容许电压动摇为:3.3*2.5%=82.5 mV,所需电容量为:

C=I*dt/dv=1.782A*2ns/0.0825V=43.2nF

阐明:所加的电容实践上作为按捺电压波纹的储能元件,该电容有必要在 2ns 内为负载供给1.782A 的电流,一起电压下降不能超越 82.5 mV,因而电容值应依据 82.5 mV 来核算。记住:电容放电给负载供给电流,其自身电压也会下降,可是电压下降的量不能超越 82.5mV(容许的电压波纹)。这种核算没什么实践意义,之所以放在这儿说一下,是为了让咱们对去耦原理知道更深。

办法二:运用方针阻抗核算电容量(规划思维很谨慎,要吃透)

为了清楚的阐明电容量的核算办法,咱们用一个比如。要去耦的电源为 1.2V,容许电压动摇为 2.5%,最大瞬态电流 600mA,

榜首步:核算方针阻抗

第二步:确认稳压电源频率呼应规模。

和详细运用的电源片子有关,一般在 DC 到几百 kHz 之间。这儿设为 DC 到 100kHz。在100kHz 以下时,电源芯片能很好的对瞬态电流做出反响,高于 100kHz 时,体现为很高的阻抗,假如没有外加电容,电源动摇将超越答应的 2.5%。为了在高于 100kHz 时仍满意电压动摇小于 2.5%要求,应该加多大的电容?

第三步:核算 bulk 电容量

当频率处于电容自谐振点以下时,电容的阻抗可近似表明为:频率 f 越高,阻抗越小,频率越低,阻抗越大。在感兴趣的频率规模内,电容的最大阻抗不能超越方针阻抗,因而运用 100kHz 核算(电容起作用的频率规模的最低频率,对应电容最高阻抗)。

第四步:核算 bulk 电容的最高有用频率

当频率处于电容自谐振点以上时,电容的阻抗可近似表明为:频率 f 越高,阻抗越大,但阻抗不能超越方针阻抗。假定 ESL 为 5nH,则最高有用频率为:。这样一个大的电容能够让咱们把电源阻抗在 100kHz 到1.6MHz 之间操控在方针阻抗之下。当频率高于 1.6MHz 时,还需求额定的电容来操控电源体系阻抗。

第五步:核算频率高于 1.6MHz 时所需电容

假如期望电源体系在 500MHz 以下时都能满意电压动摇要求,就有必要操控电容的寄生电感量。有必要满意

所以有:

假定运用 AVX 公司的 0402 封装陶瓷电容,寄生电感约为 0.4nH,加上装置到电路板上后过孔的寄生电感(本文后边有核算办法)假定为 0.6nH,则总的寄生电感为 1 nH。为了满意总电感不大于 0.16 nH 的要求,咱们需求并联的电容个数为:1/0.016=62.5 个,因而需求 63 个 0402 电容。

为了在 1.6MHz 时阻抗小于方针阻抗,需求电容量为:

因而每个电容的电容量为 1.9894/63=0.0316 uF。

综上所述,关于这个体系,咱们挑选 1 个 31.831 uF 的大电容和 63 个 0.0316 uF 的小电容即可满意要求。

相同容值电容的并联

运用许多电容并联能有用地减小阻抗。63 个 0.0316 uF 的小电容(每个电容 ESL 为 1 nH)并联的作用适当于一个具有 0.159 nH ESL 的 1.9908 uF %&&&&&%。

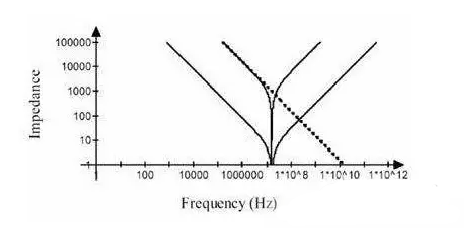

图 10 多个等值电容并联

单个电容及并联电容的阻抗特性如图 10 所示。并联后仍有相同的谐振频率,可是并联电容在每一个频率点上的阻抗都小于单个电容。

可是,从图中咱们看到,阻抗曲线呈 V 字型,跟着频率违背谐振点,其阻抗依然上升的很快。要在很宽的频率规模内满意方针阻抗要求,需求并联许多的同值电容。这不是一种好的办法,形成极大地糟蹋。有些人喜爱在电路板上放置许多 0.1uF 电容,假如你规划的电路作业频率很高,信号改变很快,那就不要这样做,最好运用不同容值的组合来构成相对平整的阻抗曲线。

不同容值电容的并联与反谐振(AnTI-Resonance)

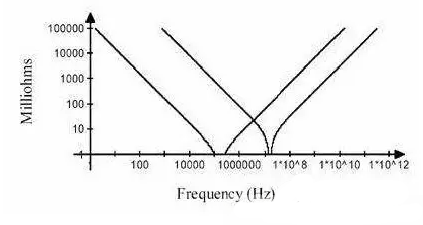

容值不同的电容具有不同的谐振点。图 11 画出了两个%&&&&&%阻抗随频率改变的曲线。

图 11 两个不同电容的阻抗曲线

左面谐振点之前,两个电容都呈容性,右边谐振点后,两个电容都呈理性。在两个谐振点之间,阻抗曲线穿插,在穿插点处,左面曲线代表的电容呈理性,而右边曲线代表的%&&&&&%呈容性,此刻适当于 LC 并联电路。关于 LC 并联电路来说,当 L 和 C 上的电抗持平时,发生并联谐振。因而,两条曲线的穿插点处会发生并联谐振,这便是反谐振效应,该频率点为反谐振点。

图 12 不同容值电容并联后阻抗曲线

两个容值不同的电容并联后,阻抗曲线如图 12 所示。从图 12 中咱们能够得出两个定论:

a 不同容值的电容并联,其阻抗特性曲线的底部要比图 10 阻抗曲线的底部平整得多(尽管存在反谐振点,有一个阻抗尖峰),因而能更有用地在很宽的频率规模内减小阻抗。

b 在反谐振(AnTI-Resonance)点处,并联电容的阻抗值无限大,高于两个电容任何一个独自作用时的阻抗。并联谐振或反谐振现象是运用并联去耦办法的不足之处。在并联电容去耦的电路中,尽管大多数频率值的噪声或信号都能在电源体系中找到低阻抗回流途径,可是关于那些频率值挨近反谐振点的,因为电源体系体现出的高阻抗,使得这部分噪声或信号能量无法在电源分配体系中找到回流途径,终究会从 PCB 上发射出去(空气也是一种介质,波阻抗只要几百欧姆),然后在反谐振频率点处发生严峻的 EMI 问题。

因而,并联电容去耦的电源分配体系一个重要的问题便是:合理的挑选电容,尽可能的压低反谐振点处的阻抗。

ESR 对反谐振(AnTI-Resonance)的影响AnTI-Resonance 给电源去耦带来费事,但走运的是,实践状况不会像图 12 显现的那么糟糕。

实践电容除了 LC 之外,还存在等效串联电阻 ESR。

因而,反谐振点处的阻抗也不会是无限大的。实践上,能够经过核算得到反谐振点处的阻抗,X 为反谐振点处单个%&&&&&%的阻抗虚部(均持平)。