S3C2440的LCD编程

1. LCD作业的硬件需求:

要使一块LCD正常的显现文字或图画,不只需求LCD驱动器,并且还需求相应的LCD操控器。在通常情况下,出产厂商把LCD驱动器会以 COF/COG的 方式与LCD玻璃基板制造在一起,而LCD操控器则是由外部的电路来完结,现在许多的MCU内部都集成了LCD操控器,如S3C2410/2440等。通 过LCD操控器就能够发生LCD驱动器所需求的操控信号来操控STN/TFT屏了。

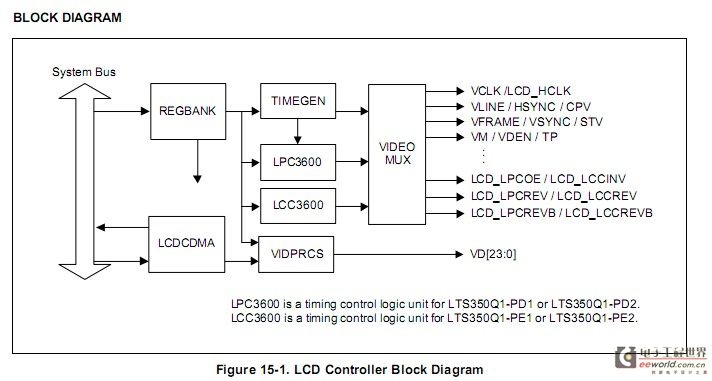

2. S3C2440内部LCD操控器结构图:

咱们依据数据手册来描绘一下这个集成在S3C2440内部的LCD操控器:

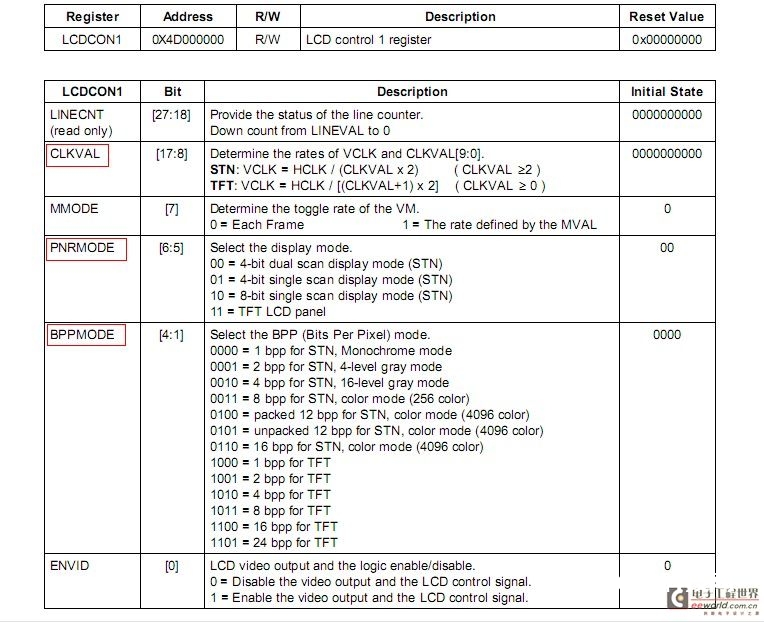

a:LCD操控器由REGBANK、LCDCDMA、TIMEGEN、VIDPRCS寄存器组成;

b:REGBANK由17个可编程的寄存器组和一块256*16的调色板内存组成,它们用来装备LCD操控器的;

c:LCDCDMA是一个专用的DMA,它能自动地把在侦内存中的视频数据传送到LCD驱动器,经过运用这个DMA通道,视频数据在不需求CPU的干涉的情况下显现在LCD屏上;

d:VIDPRCS接纳来自LCDCDMA的数据,将数据转换为适宜的数据格式,比方说4/8位单扫,4位双扫显现形式,然后经过数据端口VD[23:0]传送视频数据到LCD驱动器;

e:TIMEGEN由 可编程的逻辑组成,他生成LCD驱动器需求的操控信号,比方VSYNC、HSYNC、VCLK和LEND等,而这些操控信号又与REGBANK寄存器组中 的LCDCON1/2/3/4/5的装备密切相关,经过不同的装备,TIMEGEN就能发生这些信号的不同形状,然后支撑不同的LCD驱动器(即不同的 STN/TFT屏)。

FIFO存储器坐落LCDCDMA.。当FIFO空或部分空时,LCDCDMA要求从帧缓冲中取来要显现的图画数据,而这个帧缓冲是LCD操控 器在RAM中拓荒的一片缓冲区。当这个传输恳求被存储操控器中的总线裁定器接纳到后,从体系存储器到内部FIFO就会成功传输4个字节。FIFO的总巨细 是28个字,其间低位FIFOL是12个字,高位FIFOH是16个字。

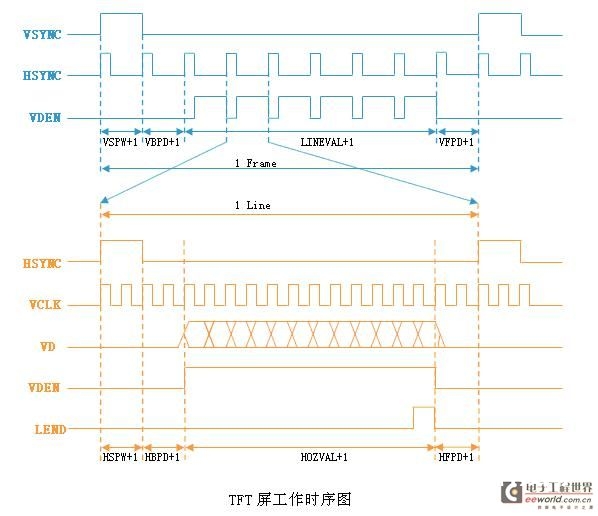

3. 常见TFT屏作业时序剖析:

LCD供给的外部接口信号:

VSYNC/VFRAME/STV:笔直同步信号(TFT)/帧同步信号(STN)/SEC TFT信号;

HSYNC/VLINE/CPV:水平同步信号(TFT)/行同步脉冲信号(STN)/SEC TFT信号;

VCLK/LCD_HCLK:象素时钟信号(TFT/STN)/SEC TFT信号;

VD[23:0]:LCD像素数据输出端口(TFT/STN/SEC TFT);

VDEN/VM/TP:数据使能信号(TFT)/LCD驱动沟通偏置信号(STN)/SEC TFT 信号;

LEND/STH:行完毕信号(TFT)/SEC TFT信号;

LCD_LPCOE:SEC TFT OE信号;

LCD_LPCREV:SEC TFT REV信号;

LCD_LPCREVB:SEC TFT REVB信号。

一切显现器显现图画的原理都是从上到下,从左到右的。这是什么意思呢?这么说吧,一副图画能够看做是一个矩形,由许多摆放规整的点一行一行组成,这些点称之为像素。那么这幅图在LCD上的显现原理便是:

A:显现指针从矩形左上角的榜首行榜首个点开端,一个点一个点的在LCD上显现,在上面的时序图上用时刻线表明就为VCLK,咱们称之为像素时钟信号;

B:当显现指针一向显现到矩形的右边就完毕这一行,那么这一行的动作在上面的时序图中就称之为1 Line;

C:接下来显现指针又回到矩形的左面从第二行开端显现,留意,显现指针在从榜首行的右边回到第二行的左面是需求必定的时刻的,咱们称之为行切换;

D:如此类推,显现指针就这样一行一行的显现至矩形的右下角才把一副图显现完结。因而,这一行一行的显现在时刻线上看,便是时序图上的HSYNC;

E: 然 而,LCD的显现并不是对一副图画快速的显现一下,为了继续和安稳的在LCD上显现,就需求切换到另一幅图上(另一幅图能够和上一副图一样或许不一样,目 的仅仅为了将图画继续的显现在LCD上)。那么这一副一副的图画就称之为帧,在时序图上就表明为1 Frame,因而从时序图上能够看出1 Line仅仅1 Frame中的一行;

F:相同的,在帧与帧切换之间也是需求必定的时刻的,咱们称之为帧切换,那么LCD整个显现的进程在时刻线上看,就可表明为时序图上的VSYNC。

上面时序图上各时钟延时参数的意义如下:(这些参数的值,LCD发生厂商会供给相应的数据手册)

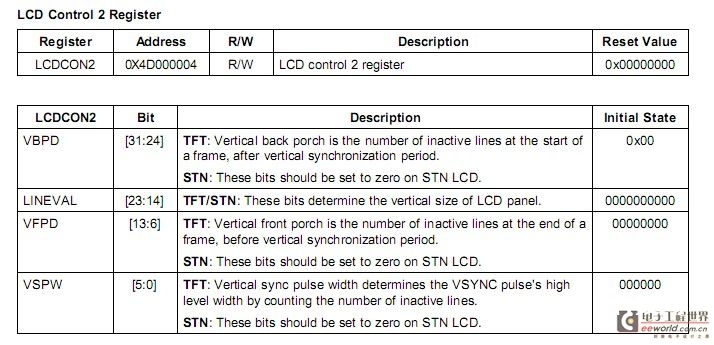

VBPD(vertical back porch):表明在一帧图画开端时,笔直同步信号今后的无效的行数,对应驱动中的upper_margin;

VFBD(vertical front porch):表明在一帧图画完毕后,笔直同步信号曾经的无效的行数,对应驱动中的lower_margin;

VSPW(vertical sync pulse width):表明笔直同步脉冲的宽度,用行数核算,对应驱动中的vsync_len;

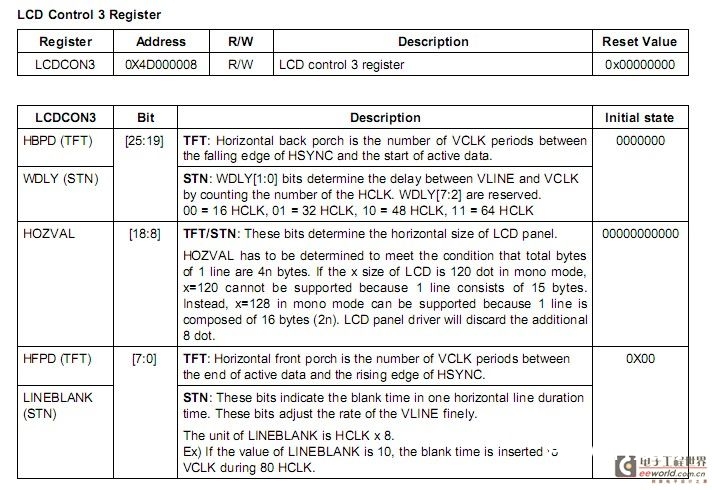

HBPD(horizontal back porch):表明从水平同步信号开端到一行的有用数据开端之间的VCLK的个数,对应驱动中的left_margin;

HFPD(horizontal front porth):表明一行的有用数据完毕到下一个水平同步信号开端之间的VCLK的个数,对应驱动中的right_margin;

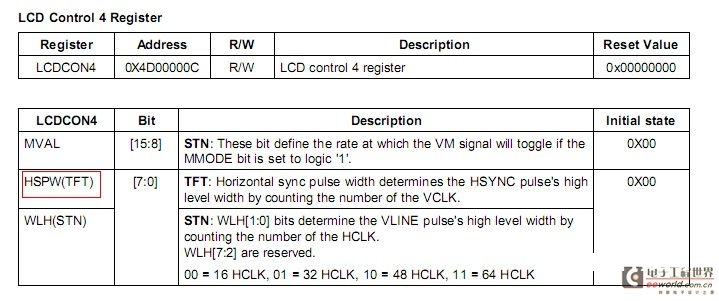

HSPW(horizontal sync pulse width):表明水平同步信号的宽度,用VCLK核算,对应驱动中的hsync_len;

注:关于一个已知尺度的LCD屏,只需确认了VCLK值,行频和场频就应该知道了。但这样还不可的,由于在每一帧时钟信号中,还会有一些与屏显现无关的时钟呈现,这就给确认行频和场频带来了必定的复杂性。如在HSYNC信号先后会有水平同步信号前肩(HFPD)和水平同步信号后肩(HBPD)呈现,在VSYNC信号先后会有笔直同步信号前肩(VFPD)和笔直同步信号后肩(VBPD)呈现,在这些信号时序内,不会有有用像素信号呈现,别的HSYNC和VSYNC信号有用时,其电平要坚持必定的时刻,它们别离叫做水平同步信号脉宽HSPW和笔直同步信号脉宽VSPW,这段时刻也不能有像素信号。因而核算行频和场频时,必定要包含这些信号。