摘要 运用FPGA IP核规划了一种快速、高效的傅里叶改换体系。针对非整数倍信号周期切断所导致的频谱走漏问题,提出了一种经过期输入信号加窗处理来按捺频谱走漏的办法。运用Modelsim和Matlab对规划计划进行了仿真,一起在Altera公司的CycloneⅡ硬件渠道进步行了验证。验证成果表明,体系功能杰出,改善作用显着。

FFT是离散傅里叶改换(DFT)的一种快速算法,被广泛应用于频谱剖析、音频编码、图画处理等数字信号处理范畴。FFT运算杂乱,需求很多的存储器和运算单元,其硬件完结渠道多种多样。DSP需求外置存储器和特定接口,约束了运算速度。ASIC虽能满意速度要求,但其硬件电路杂乱、可扩展性差、且价格昂贵。FPGA具有陕速并行运算、高集成度、低功耗等特色,且具有丰厚的IP核资源,便利调用,合适FFT算法的完结。

关于512点FFT处理器,假如该512个输入数据不是信号周期的整数倍,即非整数倍周期切断,则会呈现频谱走漏现象。窗函数处理的主旨是减小频谱走漏。惯例的FFT硬件完结办法均不考虑因为非整数倍切断导致的频谱走漏问题。针对以上问题,本文规划了一种根据Altera IP核的512点FFT体系,一起经过对输入信号的加窗处理,按捺了非整数倍信号周期切断所发生的频谱走漏。

1 原理概述

1.1 FFT原理

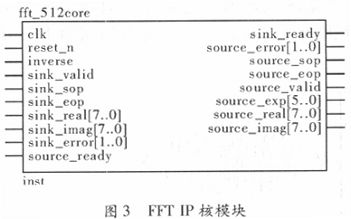

离散傅里叶改换(DFT)算法为

FFT为DFT的快速算法,其办法多种多样,根本能够分为按时刻抽取法和按频率抽取法两类。此处介绍基-4频率抽取法。令N=4M,对式(1)N点的DFT可按如下办法作按频率出抽取

4个等式可定义为一个蝶形运算,蝶形运算可看作基-4FFT根本运算单元。参加蝶形运算的4个节点是有规则的,别离为(n)、(n+N/4)、(n+2N/4)和(n+3N/4)。接着再将X(4r)、X(4r+1)、X(4r+2)和X(4r+3)别离分解为4个长度为N/16的序列,根本结构是每一级的运算由N/4个蝶形运算构成,经过迭代log4N次后完结核算。FFT算法的实质是运用系数

的共轭对称性和周期性,将长序列DFT分解成短序列DFT,避免了很多的重复运算,然后进步运算功率。

1.2 窗函数原理

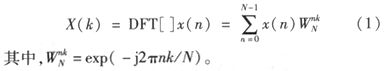

当对输入信号非整数倍周期切断,即512个输入数据不是输入信号周期的整数倍时,会呈现频谱走漏现象。对输入信号进行加窗处理,能够有用地按捺频谱走漏。常用的窗函数有矩形窗(Rectangle Window)、汉宁窗(Hanning Window)、海明窗(Hamming Window)、布拉克曼窗(Blackman Window)等,不同的窗函数具有不同的特色,表现在主瓣旁瓣宽度,频率辨认精度及起伏辨认精度等方面。图1为Matlab仿真图,别离为原始信号,原始信号加窗(海明窗)成果,原始信号做512点FFT成果,原始信号加窗后再做512点FFT成果,这4幅图直观形象地描绘了时域信号做FFT后的频域成果,以及原始信号是否加窗对FFT成果的影响。

2 FFT IP核

FFT IP核是高速履行的,参数可装备的FFT处理器,能够完结复数方式的FFT改换和IFFT改换。想要正确地运用FFT IP核,首要需求了解其引擎结构、数据流结构和要害管脚信号。

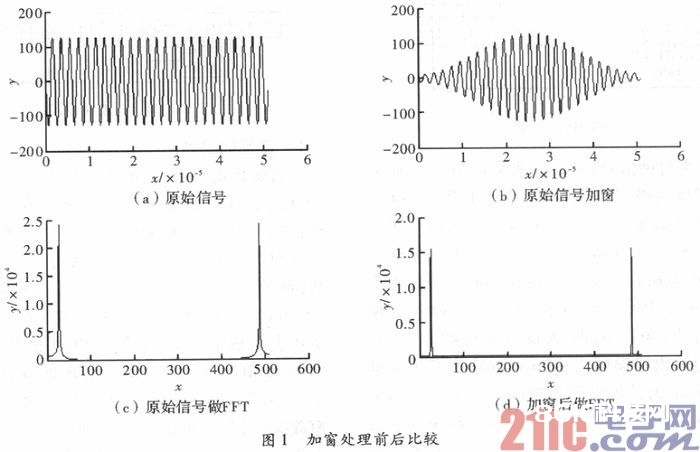

2.1 引擎结构

FFI IP核有两种不同的引擎结构:四输出和单输出,结构如图2(a)和图2(b)所示。中心差异在于FFT蝶形处理器的吞吐量。一个时钟周期内,四输出结构能够核算出一切4个蝶形输出,单输出结构能够核算出一个蝶形输出。

2.2 数据流结构

FFI IP核支撑流、变量流、缓冲突发、突发4种数据流结构。流结构答应接连输入数据,一起输出接连的复数数据流。变量流发生一个与流结构相似的接连输出数据流。缓冲突发结构需求存储资源相对较少,但均匀吞吐量也相应下降。突发结构的履行进程与缓冲突发结构相似,关于给定的参数设置,突发结构需求更少的存储资源。

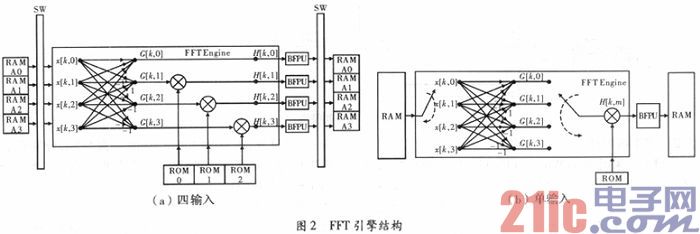

其间,clk为时钟信号;reset_n为复位信号;inverse为FFT处理器改换形式挑选信号,挑选FFT或IFFF;sink_valid为输入数据有用信号;sink_sop为输入第一个数据标志信号;sink_eop为输入最终一个数据标志信号;sink_real为输入实部数据;sink_imag为输入虚部数据;sink_error为输入过错标志;source_ready为输出等候状况标志;sink_ready为输入等候状况标志;source_error为输出过错标志;source_real为成果实部数据;source_imag为成果虚部数据;source_exp为成果补偿系数;source_valid为成果有用信号;source_sop为

输出第一个数据标志信号;source_eop为输出最终一个数据标志信号。

3 计划规划

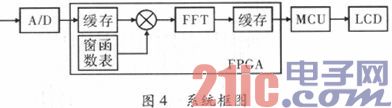

体系主要由三部分组成:A/D收集模块、FPGA处理模块及MCU运算显现模块,体系框图如图4所示。A/D收集外部信号数据,将其存入FPGA内部缓存RAM。当FFT输入有用时,读取缓存中的数据,一起与窗函数表中的对应系数做乘法运算,成果输入FFT核中,FFT核处理完毕后将数据存入缓存RAM中。单片机读取缓存RAM中的成果数据,进行相应的模值核算,并经过LCD显现成果频谱图形。该计划的中心在于窗函数与FFT运算核的规划与完结。

3.1 窗函数规划

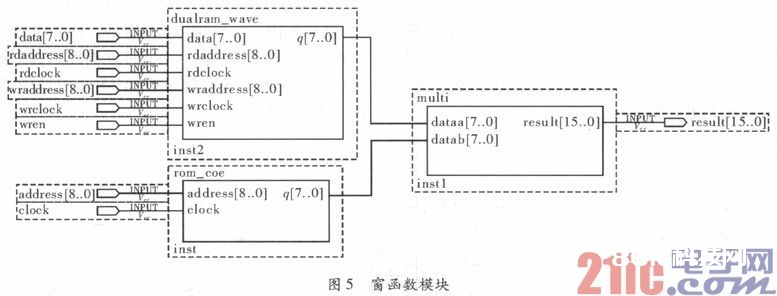

前端数据缓存选用双口RAM核,深度512,位宽8 bit,寄存A/D收集到的信号数据。窗函数表选用ROM核,深度512,位宽8 bit,寄存窗函数数据。经过Matlab生成512点Hamming窗函数系数表,因为该数据为浮点数,而本规划中悉数选用定点运算,故对窗函数系数进行256倍扩大,将其变为定点整数,数据规模为0~255。将系数表生成mif文件,作为ROM的初始化文件。该RAM和ROM选用同一套读出地址,确保相应数据同步读出,做乘法运算,得到16 bit成果数据。因为Hamming窗数据是实践数据的256倍,所以需求对乘法成果进行右移8位操作,得到8bit FFT输入数据。规划模块如图5所示,该模块完结了输入信号数据的加窗处理。

3.2 FFT核规划

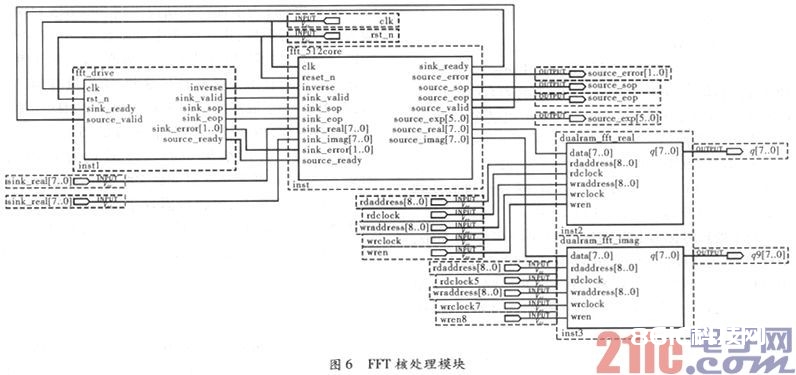

FFT核选用MegaWizard FFT v11.1,改换点数挑选512,数据精度8 bit,引擎结构挑选单输出结构,引擎数为1,I/O数据流结构挑选突发(Burst)结构。FFT输出数据有3种:实部数据、虚部数据和补偿指数数据。选用两个双口RAM核,深度均为512,宽度均为8 bit,别离寄存

FFT核的实部成果数据和虚部成果数据。因为每512个FFT输出数据,补偿指数均相同,所以设置一个8 bit的寄存器寄存补偿指数即可。规划模块如图6所示,该模块完结了加窗处理后的信号数据的快速傅里叶改换。

4 仿真与硬件验证

4.1 体系仿真

FPGA开发环境为QuartusII 11.1,仿真环境为Modelsiml0.0。仿真时,由Matlab生成波形数据mif文件,作为仿真测验数据文件存入波形缓存RAM中。经过Quartus II调用Modesim对测验工程进行仿真,仿真时序如图7所示。经时序剖析可知,作业时钟频率为100 MHz(period= 10 ns),每进行一次512点处理到悉数输出处理成果共耗时36.9μs。

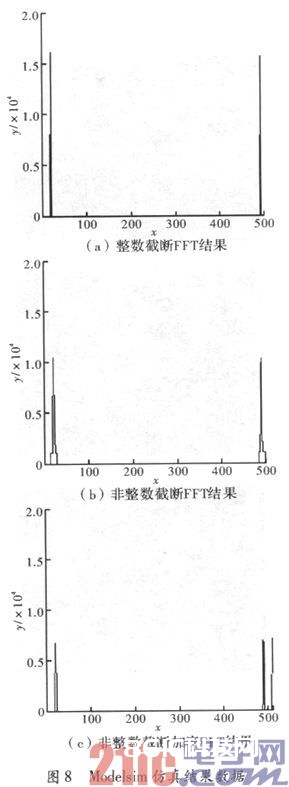

将仿真成果数据导入Matlab,得到成果由图8(a)知,对信号周期整数倍切断FFT处理后,得到单一的正确的频谱图;如图8(b)知,对信号周期非整数倍切断FFT处理后,频谱呈现严峻走漏,且起伏值下降;如图8(c)知,对信号周期非整数倍切断,加窗后做FFT处理,频谱走漏现象有显着的改善,但起伏值因为加窗处理而相应下降。仿真成果表明,FFT体系规划正确,且加窗处理对信号周期非整数倍切断导致的频谱走漏问题有杰出的改善作用。

4.2 硬件验证

ADC选用ADS9238,它是一款高速高动态规模A/D转换器,12 bit,最高采样时钟达65 MSample·s-1。MCU选用c8051F120单片机,LCD选用ZLG320240K-FFSSWE-YBC,分辨率为320×240,能够满意字符、汉字及图形等各种显现需求。FPGA选用Altera公司的Cyclone II EP2C8Q208 C8N,该芯片资源丰厚,包括8256个LEs,36个4 kbit Block RAM,18个内部乘法器和208个I/O资源,并支撑FFT IP核。

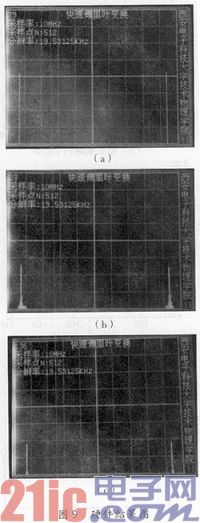

FFT处理时钟为100 MHz,A/D采样率为10 MHz,采样点数为512,故频谱分辨率f=10 MHz/512=19.531 kHz。当输入信号为390.625 kHz时,512个采样点表明20个信号周期;当输入信号为400.390 kHz时,512个采样点表明20.5个信号周期。在加窗和不加窗两种情况下别离对频率为390.625 kHz和400.390 kHz的正弦信号进行采样,得到如图9的成果。

图9中(a)为不加窗的情况下对390.625 kHz的输入信号进行采样,因为512个点正好是20倍切断,所以只在频谱的第20个点有单一幅值,阐明FFT体系作业正常。并且因为是整数倍切断,成果没有频谱走漏;图9(b)为不加窗的情况下对400.390 kHz的输入信号进行采样,因为512个点正好为20.5倍切断,非整数倍切断,所以成果中存在严峻的频谱走漏;图9(c)为加窗的情况下对400.390 kHz的输入信号进行采样,能够看到,频谱走漏现象得到较好的改善。硬件测验成果表明,FFT体系规划正确,且加窗处理对信号周期非整数倍切断导致的频谱走漏问题有杰出的改善作用。

5 完毕语

本文运用Altera公司的IP核规划了一种FFT体系,该办法规划简略、资源运用率高、运算速度快,实验证明具有杰出功能。一起针对非整数倍周期切断导致的频谱走漏问题,提出了一种经过加窗改善的办法,经硬件渠道验证,其改善作用显着。因为加窗导致的幅值改变问题,本文尚未作具体证明,有待进一步的研讨。