作者:皮代军,张海勇,叶显阳,秦水介

1导言

在科学技能研究和工业出产的各行业中,常常需求对各种数据进行收集,如液位、温度、压力、频率等信息的收集。跟着数字技能的开展,一些高功用的FPGA(FieldProgrammableGateArray)和高速的A/D使用于数据收集体系中,大大提高了体系的丈量精度、数据收集处理速度、数据传输速度等。本文规划了一种使用EP1K10TC100FPGA和单片机的数据收集体系。该体系具有数据收集速度高、功耗低、数据传输便利等长处。

2规划规划

依据FPGA的数据收集体系的整体功用模块如下图1所示。体系有由FPGA、串行被迫装备模块、USB通讯模块、电源模块、显现模块、模数转化模块、数模转化模块等几个模块组成。

主控芯片选用ACEX1K系列的EP1K10TC100-3。ACEX系列是当今AlteraCPLD中使用远景最好的器材系列之一[1,2],该系列的FPGA由逻辑阵列块LAB(Logicarrayblock)、嵌入式阵列块EAB(embeddedarrayblock)、快速互联以及IO单元构成,每个逻辑阵列块包括8个逻辑单元LE(logicelement)和一个部分互联。每个逻辑单元则由一个4输入查找表(LUT)、一个可编程触发器、快速进位链、级连链组成,多个LAB和多个EAB则可经过快速通道相互衔接[3]。EAB是ACEX系列器材在结构规划上的一个重要部件,他是输入端口和输出端口都带有触发器的一种灵敏的RAM块,其首要功用是完成一些规划不太大的FIFO、ROM、RAM和双端口RAM等。

3体系硬件规划与完成

3.1数据收集模块

体系数据收集选用DAC0832。ADC0832是美国国家半导体公司出产的一种8位分辩率、双通道A/D转化芯片,最高分辩可达256级,能够习惯一般的模仿量转化要求。其内部电源输入与参阅电压的复用,使得芯片的模仿电压输入在0“5V之间。芯片转化时刻仅为32μS,据有双数据输出可作为数据校验,以削减数据误差,转化速度快且安稳功用强。独立的芯片使能输入,使多器材挂接和处理器操控变的愈加便利。经过操控数据输入端,能够简单的完成通道功用的挑选。

3.2串行被迫装备模块

由于依据SRAM工艺FPGA存在掉电易失性特色,所以装备模块的首要是在每次上电后对FPGA进行重新装备[4]。编程文件能够放在通用程序存储器中,在FLEX器材上电后,由芯片外部操控器自动地从通用存储器中读出编程文件并送到FLEX器材进行装备,数据传送方法能够为串行,也能够为并行。被迫串行(PS)装备形式的装备接口衔接到芯片的5个引脚,别离为:nSTATUS、nCONFIG、CONF_DONE、DCLK、DATA0。ICR电路原理如图2所示。

ICR操控电路的作业进程为:经MAXPLUSII编译出产的装备文件(.sof)经过格局转化成为(.rbf)。然后,经过PC机的串行通讯口,经AT89C2051单片机操控存储在AT24C256中。单片机再依据体系的要求,经过P1.2、P1.3、P1.4、P3.0和P3.1等5个I/O口,将其存储在AT24C256中的装备数据下载到电路中的FPGA器材中去。

3.3USB通讯模块

USB接口芯片选用ISP1581。该芯片全面契合USB2.0标准,具有高速的并行通用接口,可在高速形式下作业,理论最高传输速度到达480Mbps[5]。除了操控端点外,ISP1581还有7个输入(IN)端点和7个输出(OUT)端点。每个端点能够灵敏装备数据传输方法以及数据缓存区(FIFO)的巨细,端点FIFO最大容量能够到达2KB。ISP1581芯片在装备枚举时需求单片机固件的支撑,一旦正确完成了装备和驱动加载,单片机关于ISP1581芯片就好像一般存储器相同能够进行读写操作,以发送或接纳数据。

3.4显现模块

LED选用四位共阳极数码管显现。共阳极四位一体数码管选用动态扫描作业方法,在数码管中每一位的字段位a、b、c、d、e、f、g和dp别离衔接在一起,其作业原理与共阴极数码管作业原理共同,只不过共阳极输入数码管的发光电平(有用电平)是0,和共阴极数码管相反。在数码管显现电路中运用了一个驱动芯片74LS47,运用这个驱动首要处理如下几个问题:(1)电平正负转化,(2)译码,能够节省I/O口的占用。74LS47承受四位BCD码输入,并经过7个与/或门译码后输出,用于驱动数码管,其输出的低电平驱动共阳极数码管,低电平输出电流在24mA以上。

3.5电源模块

该规划中内核电压和I/O口电压都选用2.5V.由于该芯片对电源要求很严厉,所以经过稳压块来完成电源转化。在该电路中经过一片1117-2.5稳压块由5V转化而来。电路衔接快捷简略,输出电流能够到达1A,基本上能满意该体系的需求。

4被迫串行装备程序规划

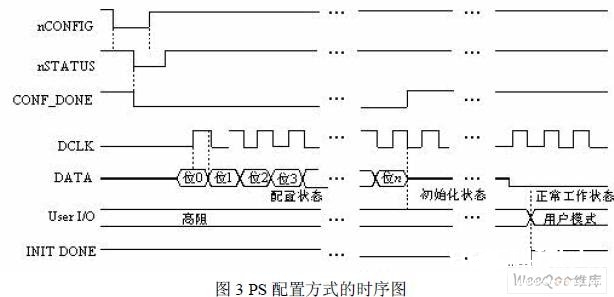

PS装备方法的时序图如图3所示。

装备前有必要先设置该芯片EP1K10TC100-3上的下载形式挑选引脚MSEL1、MSEL0。设置方法:当MSEL1=0,MSEL0=0时体系为PS或AS形式当MSEL1=1,MSEL0=0时体系为PPS形式,当MSEL1=1,MSEL0=1时体系为PPA形式。在这里设置成使MSEL1=0、MSEL0=0在PS装备进程中:当nCONFIG发生下降沿脉冲时发动装备进程,在DCLK上升沿,将数据移入方针芯片中。

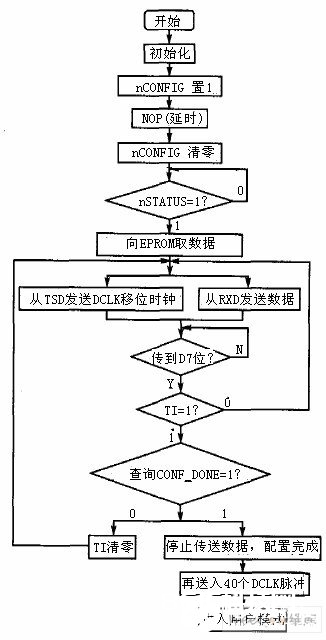

在装备进程中,体系需求实时监测,一旦犯错,nSTATUS将被拉低,体系识别到这个信号后,当即重新发动装备进程。装备数据悉数正确地移入方针芯片内部后,CONF_DONE信号跳变为高,尔后,DCLK有必要供给几个周期的时钟(详细周期数与DCLK的频率有关),保证方针芯片被正确初始化,进入用户作业形式。装备流程图如图4所示:

图4被迫串行装备流程图

5总结:

本文立异点:体系选用ACEX1K系列的EP1K10TC100-3FPGA作为操控和处理的中心,简化了体系的硬件规划,具有功耗低、速度快等长处;选用依据微操控器的FPGA器材的%&&&&&%R操控体系,具有线路结构简略、开发简单、体积小、成本低的长处;选用USB与上位机通讯,替代传统的串口数据传输,提高了数据传输速率和可扩展性,并且USB能够总线供电,在数据收集体系中耗电量小。

责任编辑:gt