Analog Devices AD5422 16 bit串行输入DAC能够设定为电压输出或电流输出。为了与DAC通讯并发生一个可变输出,就需求一个数据SERDES(串行器/解串器)。不过,假如你的规划需求一个稳定的4mA输出,能够用两只触发器对该器材作设定,并用一个机械式按键开关S1作测验(图1)。

图1按下并开释S123次今后DAC发生一个4mA的接连电流输出

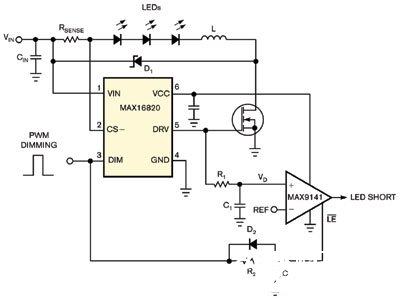

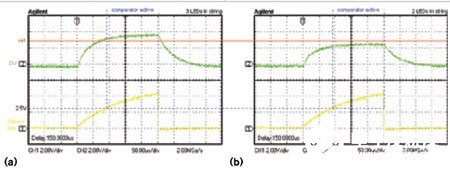

AD5422的编程设定运用24 bit长的字,其高8位构成操控寄存器的地址,低16位设定DAC的输出规模、压摆率步长和压摆率时钟(表1)。向AD5422中写入一个24bit的 0101 。.. 01方式,将其设定在一起挑选的电流区间的底部,即输出电流脚(Pin 19)上4 mA~20 mA。AD5422内部移位寄存器的数据在每次锁存信号(Pin 7)的低-高跃变时移入数据寄存器。在IC1上电后第23次按下并松开开关时,器材将这个不断替换的码序列解析为一个操控指令。该序列今后,SCLK信号能够坚持为闲暇(图2)。

图2尽管操控指令序列至少有23个时钟的宽度但能够很简单生成替换的位格局

触发器FF1装备为一个熟知的除2计数器,发生所需求的替换序列。手动按下并开释按键开关时,就能够生成一个SCLK信号。这儿有必要运用一个除颤器,由于电路需求一个洁净的SCLK逻辑信号,它的电平转化不超越数十纳秒。FF2用作一个异步置位/复位触发器,消除按键发生的信号颤抖。

为使电路正常作业,在SCLK低-高跃变后,锁存信号的有用低-高跃变有必要呈现至少13 ns。选用SN74HC74级触发器能够满意这个要求。IC2中FF1的Q输出衔接到IC1的SDIN输入。SDIN输入端的电平跃变有必要预置,并在 SCLK信号的低-高跃变时坚持至少5 ns时刻。从AD5422的精细5V基准能够取得IC1输出端FAULT(Pin 3)的上拉电阻和IC2的5V电源电压。当IC1的漏极开路FAULT输出有用时,在初始状况、给IC1操控字时钟或毛病状况时会由于负载而呈现细小的电流浪涌。所幸,输出电流(Pin 19)没有活动,不然过热条件或过大负载电阻会从外部损坏这一电流的精度。不管哪种状况,内部基准源的外部加载(不超越数十秒时刻的微安级)都不会损及基准源的精度。

表1操控指令各位的效果

经过在IOUT脚与地之间衔接一只100Ω高精度电阻,并发生23个时钟脉冲,能够测出这只电阻上的一个0.400xV电压,其间x≤4,承认这是4 mA的高精度稳定电流。IC1的实践全量程差错远小于其确保的±0.3%满量程差错最差值(参考文献1)。

因而,有必要将取得的4 mA电流相对差错(该值不大于0.1%)除以4,由于电流的标尺是20 mA–4 mA=“16” mA。所以,这种状况下DAC的全量程总差错就小于0.1%/4,即0.025%。选用单片DAC构建的恒流源,能够得到高的分辨率和可忽略不计的温度敏感度,能反抗电源电压动摇,并且有高的初始精度。电流输出DAC亦有数十兆欧的输出电阻。

电路运用S1发生只用于测验意图的SCLK信号。关于移动电源使用,能够选用一个频率高达200 kHz的自在时钟。能够从AD5422的DVCC脚为FAULT输出的上拉电阻和IC2供电。

责任编辑:gt