声响信号无处不在,一起也包含着很多的信息。在日常的出产日子中,咱们剖析声响信号,便能够简化进程,得到咱们想要的成果。跟着 DSP芯片的性价比不断攀升,使 DSP得以从军用范畴拓宽到民用范畴,由于 TI公司 DSP5000系列强壮的音频紧缩才干,语音运用得到了较大的开展。因而,根据 DSP的声响收集体系的规划与开发具有重要的现实意义。

该体系经过收集声响信号来检测器械的裂纹、密合度等。将 DSP高速处理数字信号的才干与 USB高速传输数据的才干结合起来,使其服务于工业出产,是该体系的首要规划意图。体系选用了 TI公司的TMS320VC5402作为该块 PCB的 CPU,并将Philips公司的PDIUSBD12作为接口芯片,运用 USB1.1协议进行 DSP与电脑的通讯。 硬件规划思维人类能够听到的声响信号是范围在 20-20kHz的模拟信号,所以首要需求传感器接纳该声响信号,接着需求进行转化,使声响信号由模拟信号变为数字信号。之后经过剖析噪声发生的原因和规则,运用被测信号的特色和相干性,检测被掩盖的声响信号。在检测办法上有频域信号的相干检测、时域信号的堆集均匀、离散信号的计数技能、并行检测等办法。

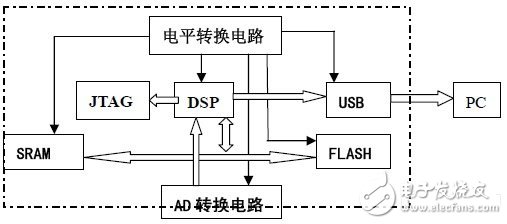

DSP与计算机的通讯,一般选用 USB、RS232、PCI或 ISA卡等方法。RS232的首要缺陷是:速度慢,不支撑热插拔; PCI与 ISA卡的首要缺陷是:受计算机卡槽数量、地址等资源的约束,可扩展性差。而运用 USB通讯的首要长处,便是传输速度快,支撑热插拔,占用资源少,可扩展性强。该规划运用 USB接口芯片直接与 DSP相连,经过 DSP的程序完结 USB的协议,最大的长处便是能够保证数据交换的速度。综上,在本体系中,几个根本环节便是:电平转化电路:将 5V电源转化为 3.3V与 1.8V,别离为 DSP芯片的片上外设以及 CPU供电; AD信号转化电路:将传感器接纳到的模拟信号转化为数字信号,供 DSP进行处理;信号的存储电路:贮存 DSP处理的信号;信号传输电路:将经过处理的信号上传至电脑;仿真电路:用于测验 DSP芯片。全体架构如图 1所示。

本体系中 DSP选用的是 TI公司的 TMS320VC5402(以下简称 5402),其操作速率达 100 MIPS,由于其具有改善的哈佛结构,所以它能够在一个指令周期内完结 32x32bit的乘法,亦能够敏捷完结数学运算最常用的乘加运算。它有 4条地址总线、3条 16位数据存储器总线和 1条程序存储器总线, 40位算术逻辑单元 (AIU),一个 17&TImes;17乘法器和一个 40位专用加法器。8个辅佐寄存器及一个软件栈,答应运用最先进的定点 DSP的 C言语编译器,内置可编程等候状况发生器、锁相环(PLL)时钟发生器、两个多通道缓冲串行口、一个 8位并行与外部处理器通讯的 HPI口、2个 16位定时器以及 6通道 DMA操控器,特别合适电池供电设备.

电平转化电路

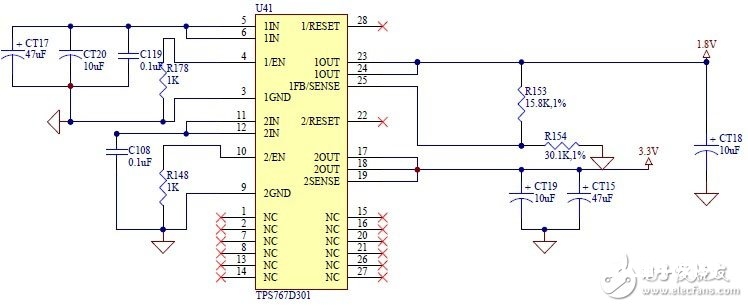

电平转化电路,望文生义,便是将电源供电的电压转化为合适芯片作业的电压。由于 5402的核电压与片上外设电压不同,并且整个电路需求的电压并不能由电源直接供给,所以电平转化电路能够说是整个电路作业的动力,为各个元器材供给合适其作业的条件。在该电路中,电源芯片运用的是 TI公司的 TPS767D301(以下简称 D301)。D301是一款能够使不同电压别离输出的芯片,可输出 3.3V和介于 1.5-5.5V之间的某一调整后的电压。由于 5402的外设电压是 3.3V,核电压为 1.8V,所以在此规划中,将该芯片的输出设定为

3.3V和 1.8V,与 5402匹配。衔接图如图 2所示。

在 1OUT的输出部分 Vo=Vref×(1+R1/R2),在 D301中,Vredf=1.1834V,所以 Vo=1.1834V×(1+15.8/30.1)=1.8V。

AD转化

本规划中选用的 AD转化芯片是 TI公司的 TLC320AD50C。该芯片的采样选用ΣΔ技能,行将一个抽样滤波器放置于 ADC后,将一个差值滤波器放置在 DAC前。这种结构的最大特色便是使体系可一起进行接纳、发送使命。 TLC320AD50C可完结高采样率(最高可达 22.5kb/s)的 AD/DA转化,该功用由 2个 16位的同步串行转化通道完结,可直接和 DSP衔接进行通讯。TLC320AD50C中的可选项和电路装备能够经过串行口进行编程,该芯片对掉电、复位、信号采样率、串行时钟率、增益操控、通讯协议、测验形式等可经过串行口进行编程和电路装备。详细衔接如图 3:

片外复位电路供给上电复位,晶振电路可供给 10MHz的主时钟频率,数据采样频率和其他时钟信号均由此频率分配。5402与 AD50C之间的通讯格局为主串行通讯格局:接纳和发送转化信号。

存储收集到声响信号后,一个很重要的环节便是声响信号的存储,本体系中咱们选用的是SST公司的 FLASH存储器: SST39VF400A。该器材存储容量为 4 MB,选用 3.3 V单电源供电,对各个子模块的读写和擦除,可经过一些特别的命令字序列来完结且无需额定供给高电压。在此规划中咱们运用 DSP编程完结对该存储器的读写操作。DSP首要经过外部存储器接口 (EMIF)拜访片外存储器。它不只具有很强的接口才干(能够和各种存储器直接接口),并且具有很高的数据吞吐才干。 5402与 SST39VF400的接口电路规划如图 1所示。该电路首要经过 DSP的相关输出管脚来操控 FLASH的擦除和读写。其间,A0~A19为地址线,DQ0~DQ15为数据线,OE和 WE别离为输出使能和写使能, CE1为片使能。

声响信号经过 AD转化器今后传输给 DSP,由 DSP的 PS和 DS引脚经过逻辑开关来别离操控 flash和 sram的使能端,由 DSP的 R\W和 MSTRB操控位经过逻辑电路别离操控读和写。在本规划中,SRAM运用的是 GS1117:64K×16的 1MB异步静态随机存储器。 GS71116是一个由高速的互补性金属氧化物半导体晶体管( CMOS)组成的静态随机存储器,不需求外部时钟或时刻频闪观测器。 3.3V的操作电压,一切的输入输出均兼容晶体管逻辑电路(TTL)。它的快速通道时刻小于 15ns,操作电流小于 100mA。

USB

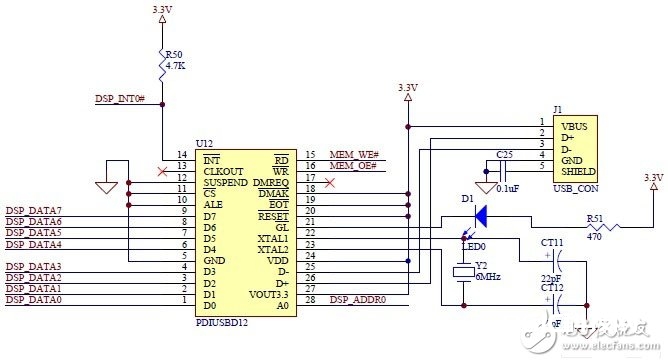

PDIUSBD12是一款带并行总线的 USB 接口器材,它契合通用串行总线 USB 1.1 版规范,集成了 SIE、FIFO、存储器收发器以及电压调整器等,可与任何外部微操控器或微处理器完结高速并行接口 2M字节/秒,且在批量形式和同步形式下均可完结 1M字节/秒的数据传输速率,可经过软件操控与 USB 的衔接,选用 GoodLink技能的衔接指示器 ,在通讯时使 LED 闪耀,具有可编程的时钟频率输出,内部上电复位和低电压复位电路,为双电源操作,在 3.3±0.3V或扩展的 5V电源下均可运用,可完结多中止形式的批量和同步传输。衔接图如图 4:

JTAG

JTAG是 joint test action group的简称,是用来调试 DSP的仿真部分,其衔接部分要和仿真器上的引脚共同。TI公司的DSP5000系列专门预留有JTAG管脚,共14个, 4,8,10,12引脚均接地,6引脚悬空,5接高平电压3.3V,一切的仿真引脚均运用 IEEE1149.1规范,其他的引脚意义为【5】:1、TMS:输入引脚,挑选测验方法;2、TRST:输入引脚,测验复位;3、TDI:输入引脚,测验数据输入;7、TDO:输出引脚,在 TCK的下降沿时输出数据,其他时刻呈高阻态;9、TCK_RET:输入引脚,在板子与仿真器的衔接电缆不小于 6英寸的时分,接法与 TCK相同,大于 6英寸的时分,需另加驱动;11、TCK:输入引脚,测验时钟,一般为占空比为50%的固有时钟信号;13、EMU0:仿真中止引脚0,可用作输入或输出;14、EMU1:仿真中止引脚1,可用作输入或输出,当 TRST为低电平、EMU0为高电平时,EMU1为低电平,一切输出制止。

经过这个声响收集体系,咱们能够把无形的声响信号转化为图形进行处理,能够调查它的波形特色进行研究、工业出产等等。而在规划其他的 DSP运用体系接口电路时,要根据详细情况归纳考虑性能指标、器材选取、外围电路规划等方面,细心选取器材,精心合理布局,才干到达抱负的规划作用。