更高体系功率和功率密度,是如今数据和电信电源体系规划的首要方针。为达此一意图,半导体开发商研宣布选用栅极屏蔽结构的新一代沟槽式金属氧化物半导体场效电晶体(MOSFET),可显着下降全负载及轻负载时的功率损耗。

怎么得到更高的体系功率和功率密度,是现代数据和电信电源体系的中心要害,因为一个小而高功率的电源体系,能够有用节约空间与动力费用。从拓扑结构的视点来看,变压器将交流电转化成直流电的同步整流,是许多运用中开关电源二次侧的首要模组架构,此能改进动力转化中的导通损耗和开关损耗。从元件的视点来看,功率金属氧化物半导体场效电晶体(MOSFET)在曩昔十年有长足的前进,也因而衍生出新的拓扑结构和高功率密度电源。同步整流MOSFET之首要需求如下:

。低沟槽通态电阻RDS(ON)

。低栅极电荷QG

。低反向康复电荷QRR和共源极输出电容COSS

。较不活泼的体二极体特性

。低闸漏电Qgd/栅极电荷Qgs比

封装方法影响MOS功耗

现在有半导体厂商选用栅极屏蔽(Shielded Gate)技能,规划出高功率的MOSFET,如方便半导体的PowerTrench MOSFET。本文以PowerTrench MOSFET为例,关于伺服器电源的同步整流或电信整流器的功率损耗深入分析。

。导通损耗

假如MOSFET产品的导通电阻和汲极电流低于二极体的正向电压降,同步整流的功率损耗也会较低。因而,二次侧的同步整流是进步体系功率的极佳解决方案。透过下列公式1,能够计算出导通损耗:

公式1

公式1

运用如今干流的中电压MOSFET技能,依额定电压进行TO-220规范封装,可使RDS(ON)下降至1?2毫欧姆(mohm),而高电压 MOSFET相关的封装电阻,现在则没有受到重视。不同于高电压MOSFET,中电压MOSFET的封装自身因为打线(Bonding)、接脚 (Lead)和源极金属(Source Mental)等要素,也占了总阻抗的一部分。透过Power56等SMD封装,能够显着下降中电压MOSFET的总导通电阻,并一起下降封装电感以削减电压突波。

。栅极驱动损耗

栅极驱动器驱动损耗与栅极电荷QG休戚相关。在低电压运用中,驱动损耗或许占总功率损耗的大部分,因为相较于高压开关,此刻电压开关仅有极低的导通损耗。在轻载情况下,导通损耗最小,故驱动损耗更为重要。众所周知,透过下列公式2能够计算出驱动损耗:

公式2

公式2

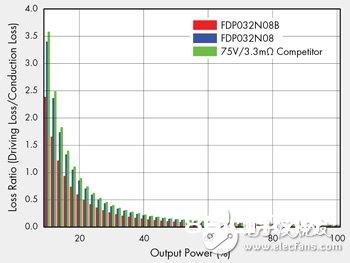

在同步整流中,电流于导通期间从MOSFET的源极流到汲极,而在死区时刻(Dead Time)则流经体二极体。因为MOSFET是软开关,在开关的敞开和封闭瞬间dVds/dt为零,所以同步整流时电源MOSFET的栅极-源极电压并没有高原区。因而,在SR、QSYNC间发生的栅极电荷,其巨细约等于栅极电荷之栅极-漏极QGD减去总栅极电荷QG。如表1所示,最新栅极屏蔽沟槽 MOSFET的QSYNC相较于传统沟槽栅极MOSFET与75V/3.3m对照元件,可别离下降28%与34%。图1显现上述三种元件的驱动损耗和导通损耗之损耗率比较。测验环境为12伏特(V)同步整流渠道,栅极驱动电压为10V,开关频率为100kHz。其间两个同步开关,在10%输出负载条件下,其栅极驱动损耗是导通损耗的三倍以上。由图1可知,栅极屏蔽MOSFET能够大大下降在轻负载条件下因为小QSYNC所发生的驱动损耗。

图1 依输出负载的损耗率比较

。体二极体损耗

在死区时刻,体二极体为导通。体二极体导通时会发生可观的功率损耗,因为相较于MOSFET通道,P-N接面形成的电压降更高。体二极体在死区时刻导通所形成的功率损耗,会显着下降全体功率,特别是在低电压和高频率时,其导通损耗可由公式3得知:

公式3

公式3

在MOSFET封闭瞬间,反向恢復电荷Qrr会消失,而共源极输出电容COSS会充电至满意二次侧的转化电压停止。二极体反向恢復电荷Qrr,在开关封闭时也会形成功率损耗。因体二极体特性发生的功率损耗可由公式4得知:

公式4

公式4

输出电容中贮存的电荷QOSS也会形成功率损耗,并与开关频率和VDS成正比。因COSS形成的功率损耗可由公式5求出:

公式5

公式5

电压突波(Spikes)的影响

实践运用中,缓冲器可用于操控最大额定漏极-源极电压之电压突波,在此情况下,额定的功率损耗是不行避免的。此外,在轻负载时缓冲器形成的功率损耗也是不行小觑。除了电路板规划的良窳,元件特性也会影响电压突波等级。在同步整流中,反向康复期间体二极体的软度便是一个首要的元件参数。二极体的反向康复特性,基本上在元件规划阶段就已决议。

寄生电感会严重影响MOSFET的开关特性,一般会导致开关损耗添加并使其违背预期的功能。因元件封装和电路Layout而发生寄生电感,为电路必定现象。封装的电感大部分源于接脚长度,业界规范的通孔TO-220封装一般会有7nH的接脚电感,但 PQFN56 SMD封装却仅有1nH。别的还有电路Layout发生的寄生电感和%&&&&&%。在电路Layout中,线距离1公分约会发生6?10nH的电感。这些寄生电感直接影响到体二极体的反向康复特性和电压突波峰值。在材料表中的体二极体康复电荷是COSS位移电流之总和,包含收回的少量载流子的电流,以及从测验电路的公共源极电感发生的反响电流。图2所示为依据各种常见源极电感模仿之体二极体反向康复进程波形;很显着地,较高的电感将导致较大的Qrr和更高的峰值电压。若是运用1nH源极电感之Power56 SMD封装,峰值电压将可从59.2V下降到55.6V。因而,怎么尽量削减源极电感,成为改进体系功率的首要要害。

图2 依据源极电感得出之体二极体的反向康复波形比较

栅极屏蔽MOSFET功能跃进

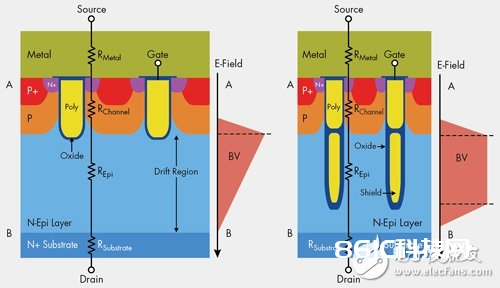

如今厂商已开宣布许多新技能,可进步RDS(ON)×QG FOM,其间首要针对导通阻抗中电压MOSFET(BVDSS

图3 传统沟槽栅极MOSFET(左)与选用屏蔽栅极技能的沟槽MOSFET(右)之笔直结构

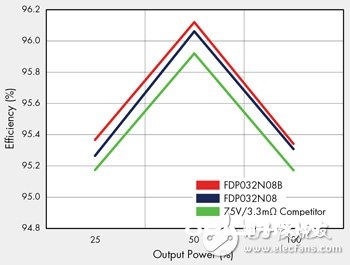

因为轻负载时的功率日益重要,栅极驱动损耗与缓冲器损耗也变得愈加重要。因而,低QSYNC与高软度的体二极体成为改进同步整流功率的重要要素。但是,RDS(on)仍是运用中的要害参数。图4显现表1中三个元件在600W相移式(Phase-shifted)全桥转化器同步整流体系的功率比较。在轻负载条件下,运用最新栅极屏蔽沟槽MOSFET的体系总功率为95.36%,在全负荷状态下则是95.34%。因为低驱动损耗和关断切换损耗,在10% 的负载下选用栅极屏蔽架构的MOSFET体系总功率,相较于传统沟槽栅极MOSFET和75V/3.3mOhm对照组,别离高出0.1%和0.19%。从图4功率比较成果显着可知,栅极屏蔽沟槽MOSFET在全负荷和轻负荷条件下,都能显着削减功率损耗,并结合小QSYNC和快速切换的软反向康复体二极体功能,能够大大进步同步整流功率。

图4 在600W时的同步整流功率比较

(本文作者Won-suk Choi/Dong-wook Kim/Dong-kook Son皆任职于方便半导体)