导言

跟着大规划集成电路的快速开展,体系规划已从传统的寻求大规划、高密度逐步转向进步资源使用率,使有限的资源能够完结更大规划的逻辑规划。使用现场可编程逻辑器材FPGA的屡次可编程装备特色,经过从头下载存储于存储器的不同体系数据,然后完结不同的芯片逻辑功用,能够在很大程度上进步资源使用率。原始装备FPGA的办法是硬件规划者依据需求规划生成装备数据流,然后经过专用装备芯片对FPGA进行装备,例如经过下载电缆将装备数据流存储到FPGA装备存储芯片中,该办法的整个进程需求芯片厂商的专用软件参加。因而,该装备办法对依靠下载电缆,适合于产品研发进程中下载装备操作,且有必定的局限性,不适用对产品应用中的体系晋级或体系重构。

结合对FPGA重装备计划的软硬件规划,本文经过PC机并经过总线(如PCI总线)将装备数据流下载到硬件功用模块的有关装备芯片,然后完结装备FPGA的全进程。该办法的软件部分依据Visual C++的开发环境,并用C++言语开发动态衔接库,以用于软件规划应用程序部分的调用。文中胪陈了上层用户对装备文件的处理、调用动态衔接库中的发送函数、将装备数据流发送给硬件的软件规划进程,并经过树立用户与硬件的握手联络,来进步装备数据的传输率。

1 FPGA的可重装备硬件计划

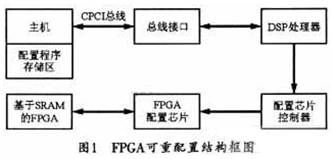

本文给出的规划计划将FPGA的装备程序文件看作一个“方针”,逻辑规划者先将所要完结的作业程序生成这样的一个“方针”,然后由上位机经过某种通讯接口模块及逻辑操控模块,将其下传到FPGA的装备芯片中来完结FPGA器材的从头装备,即经过对FPGA逻辑的重装备来完结体系的重构或晋级。逻辑规划者终究经过上位机用户界面的简略操作,即可完结硬件功用模块的作业办法重构,其可重装备的体系硬件结构框图如图1所示。

图1中借用原体系DSP处理器的操控功用来完结上位机操控指令及下载数据的接纳,上位机与体系之间选用PCI总线接口。上位机指令由DSP处理器进行解析,并随后发送到装备芯片操控器中,装备芯片操控器可由CPLD器材构成,它的编程选用EEPROM或FLASH技能,且无需外部存储器芯片。

在规划中,上位机经过PCI总线树立通讯并发送装备指令及数据至DSP,DSP以串行办法告诉装备芯片操控器发送操控指令以及要进行装备的数据包,一起,装备芯片操控器在解析指令后,还应履行相应的操作,并完结FPGA装备芯片所需的下载时序及装备数据。装备芯片的数据下载进程称为编程操作,编程完结后,再发动装备操作,即可进行FPGA从装备芯片读取新的体系装备程序进程。与常用的FPGA装备办法相比较,本文所选用的FPGA可重构规划的硬件结构愈加简略,用户操作也愈加便利,并且在对FPGA的装备芯片写入装备程序数据的时分,并不会影响到FPGA的持续作业,体系重构的时隙也更小。

DSP操控程序一般选用中止等候的规划思维,处理器上电发动后,首要对本身的作业办法进行设置,然后对体系各个功用模块进行初始化操作,使其作业在一个确认的已知状况下。之后,在完结体系的初始化今后,DSP程序进入闲暇等候状况,直到标志着上层指令已送达操控逻辑的中止信号有用,程序再从闲暇等候状况进入中止服务程序,然后判别是体系装备指令,仍是其他作业指令。若接纳到装备指令,则进入串口中止服务程序,随后判别装备指令的类别,并进入相应的子函数程序,包括装备办法、用户办法、擦除、擦除延时、写数据等多个子函数。装备办法是指体系经过发送操控指令来获取FPGA装备芯片的数据信号线、时钟信号线以及片选信号线的操控权,然后进行读写操作。调用装备办法子函数后,发送不同的指令操控字,便能够挑选装备不同的装备器材。

本体系中的逻辑电路渠道由2片Altra公司FPGA芯片构成,其对应的装备芯片别离为EPCS16和EPCS1器材,规划中,能够别离为这两片装备芯片设置各自的32位操控字。用户办法子函数可在体系对EPCS装备芯片的写数据操作完结后,经过体系发送操控指令来开释装备芯片EPCS的数据信号线、时钟信号线以及片选信号线的操控权,这样,FPGA将康复到用户所设置的作业办法。

2 可重装备软件计划

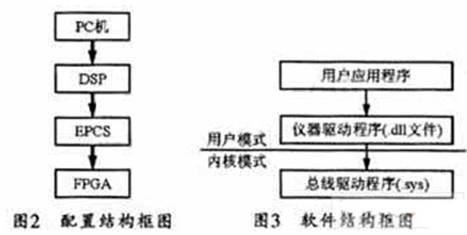

用户发送装备数据流到EPCS对FPGA进行装备的结构图如图2所示,其间PC机部分为上位机装备操控的用户软件宿主。装备操控软件首要包括用户应用程序(Win32应用程序)、仪器驱动程序、总线驱动程序三部分,总线驱动坐落整个软件体系的最底层,可经过硬件笼统层(HAL)直接与硬件进行沟通。仪器驱动坐落总线驱动和用户应用程序之间。它对上可为屏蔽底层作业细节供给应用程序调用的接口函数,对下则可发送指令或接纳数据。用户应用程序则坐落软件结构的最上层,可经过调用仪器驱动程序,间接地与底层进行交互。其结构图如图3所示。

Windows XP操作体系中的驱动程序开发首要是依据Win32办法驱动程序,即依据WDM(Win32 Driver Model)。在WDM驱动模型中,每个硬件设至极罕见两个驱动程序:总线驱动程序和功用驱动程序。其间总线驱动程序由Windows供给,需求考虑的是担任完结PCI设备逻辑功用的功用驱动程序。所以,驱动程序分为以动态链接库办法的仪器驱动程序和以WDM格局的底层的接口驱动程序。前者用于完结对方针硬件的操作,即下载装备数据流对FPGA的装备;后者则可完结资源分配、接口办理及数据的操控传输。

3装备数据剖析

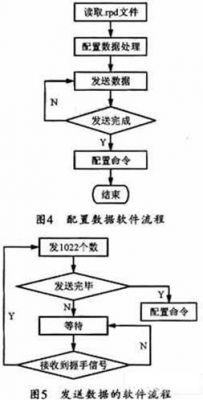

本规划中的应用软件所要下载的装备数据流是由硬件规划者依据需求供给的,是以二进制办法存储的.rpd文件。能够依据不同的FPGA来挑选不同的外围存储芯片(如EPCS1,EPCS16),然后生成不同巨细的装备数据流。由于软件规划中,每次下发的数据必定,所以,由数据流的巨细就能决议循环发送数据的次数。

由于硬件规划者供给的.rod文件中的数据并不是原始的装备数据,而是所要装备的数据经过回转生成的新的装备数据流,所以,要先将.rpd中的数据回转处理后再发送给硬件。经过用户界面能够二进制的办法翻开.rod文件并读数,将装备数据流以单字节的办法暂存在一数组中,然后对数据进行回转处理。数组中每个单字节数据的回转进程为:unsigned char strl=DE,回转后为strl=7B,界说无符号char型变量bi(i为小于8的整数),可由下面的转化完结:

由此能够得到:strl=7B。对回转处理生成的单字节数据经过组合处理后,终究便可得到对FPGA进行装备所需求的数据流。

4仪器驱动函数的规划

依据硬件规划,仪器驱动需将装备数据以长整型的办法发送,即32位。由于装备数据的长度为16位,所以发送数据时,每非必须传两个数,高16位和低16位别离放一个数。当应用程序翻开.rpd文件时,应将其间装备数据流保存在数组ww[f]中,而回转处理后得到的数据仍然放在数组ww[f]中并掩盖本来的数据,然后依据公式(1)进行组合处理,以得到终究要发送的32位数据并保存在长整型数组comdata[f]中。数组comdata[j]中的每个数据实际上包括两个装备数据,榜首个数放在高16位,第二个数放在低16位,顺次类推。确认好数据后,便能够调用动态衔接库中的发送数据函数并发送给硬件。

comdata[j]=(ww[i]24)∣(ww[i+1]16)∣(ww[i+2]8)∣ww[i+3](1)

应用程序能够经过DeviceI/OControl ( )函数和WDM进行通讯,DeviceI/OControl ( )既能够读数据,也能够写数据,常用于数据量较小的情况下。在软件规划中,发送装备数据可经过调用DeviceI/OControl()完结。依据硬件要求,每次可下发1022个装备数据到cyclone (即循环发LONG型数据511次),然后由cyclone给DSP一个中止信号,DSP接到中止信号后,即进入中止程序,开端接纳装备数据。当应用程序调用发送数据函数时,可先确认要发送的装备数据巨细,再核算发送的次数。为了尽可能的减小发送时刻,有用完结数据的发送与装备,应在软件规划中树立与底层硬件的握手联络。用户每发送1022个数据便进入等候状况,在等候期间,DSP可把接纳到的数据转化为EPCS所需求的装备数据流。当DSP处理完这段数据后,就给上层用户发送一个握手信号,用户接纳到握手信号,便进入下一个1022的发送,假如最终一次发送的数据不行1022个,则用0xFFFF补足1022个数据,如此循环处理,直到数据发送结束。发送结束后,再给硬件持续发送一个装备指令,DSP接到该指令后,又开端对cyclone进行装备,然后完结整个装备进程。图4和图5别离是装备数据和发送数据的软件作业流程。

图6为上位机装备操控界面,图中给出了2片装备芯片的装备进程,这是选用Visual C++和NIMeasurement Studio联合编程办法的规范用户界面。其间Visual C++供给了友爱的界面及用户了解的Windows风格界面,并能够调用CVI中供给的控件库和库函数。

5 结束语

本文给出了一种依据VC++程序的FPGA可重装备的完结计划,该计划在装备进程中,用户能够经过调用自己的逻辑装备文件和程序来完结处理转化,并操控下载,然后完结用户体系的FPGA在体系编程。该办法可有用进步体系装备的功率,并为产品的晋级、重构,以及用户产品二次开发供给了杰出手法。此外,凭借互联网技能,本规划还能够支撑长途下载功用。

发布者:小宇