规划工程师一般在FPGA上完成FIFO(先进先出寄存器)的时分,都会运用由芯片供给商所供给的FIFO。可是,因为其通用性使得其针对性变差,某些状况下会变得不方便或许将添加硬件本钱。

此刻,需求进行自行FIFO规划。本文供给了一种依据信元的FIFO规划办法以供规划者在恰当的时分选用。这种办法也适合于不定长包的处理。

FIFO在数字通讯芯片范畴中有两个首要的效果,缓冲数据和阻隔时钟。关于FIFO的规划,最要害的问题是怎么完成RAM的读写两边的信息交流。一般状况下,规划者都直接调用厂商为自己的FPGA专门打造的FIFO核。根本单元是FIFO所运用的RAM的一次读写操作的最小单元,如一个字节,一个字或许是一个双字。所谓操作粒度,即FIFO的读写两边的信息交流是依据这些根本单元。

ATM运用中的FIFO规划

以ATM的规划为例,在ATM的相关规划中,规划者则更多期望一个FIFO对外给出的信息是“现在FIFO中还剩余几个信元”。要完成这一功用一般有两种办法:

调用厂商供给的以操作粒度为根本单元的通用FIFO,然后在这个FIFO的外面再加上一个“套子”。这个套子里边规划一些计数器,依据计数内容对外供给相应的信息。

规划操作粒度为信元的定制FIFO。这样对外直接供给规划者最期望得到的信息,即FIFO中还有多少个信元。

设定FIFO最多能够寄存4个信元。根本单元为字节,因而RAM的数据宽度为8位,一个信元的长度为53字节。

把RAM分红4个信元区域,读写地址的高二位指明信元区域,低六位指明信元区域内的字节地址,这样组合成8位读写地址。读写两边的信息交流是相互告诉对方还有多少个信元在FIFO中。读写两边都具有自己的记分牌(Scoreboard),这个记分牌能够由一个四位的寄存器来完成,每一位对应一个信元区域。当一个信元区域中有一个完好的信元的时分,记分牌的相应的寄存器被设置为‘1’,否则为‘0’。读出方读出一个信元,修正自己记分牌的动作叫做清位。写入方写入一个完好信元,修正自己记分牌的动作叫置位。

从逻辑上说,只需求读出方把自己的记分牌的信息(清位信息)传送给写入方,一起写入方把自己的记分牌的信息(置位信息)传送给读出方就能够了,即只需构成两条逻辑通道就能够满意需求。可是,在硬件上的完成却要比这种只从逻辑上的考虑要杂乱。因为读写两边有或许处在不同的时钟域,所以当读写两边交流信息的时分就需求处理信号采样的亚稳态状况。咱们运用下面的办法来处理信号亚稳态。

消除信号亚稳态

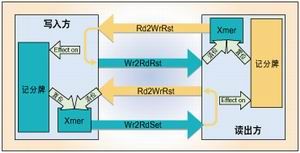

在读、写入方之间树立下面的四条单向数据通道:传送写入方到读出方的置位信息(Wr2RdSet);写入方到读出方的清位信息(Wr2RdRst);读出方到写入方的清位信息(Rd2WrRst);读出方到写入方的置位信息(Rd2WrSet)。因为读出方只发生清位信息,而写入方只发生置位信息,所以信息自身只要两个。四条通道能够被划分为两个信息组:一个组(Rd2WrRst和Wr2RdRst)传递清位信息,叫清位信息组;一个组(Wr2RdSet?和Rd2WrSet)传递置位信息,叫置位信息组。读出方运用清位信息组,写入方运用置位信息组。这样做的意图是为了树立起一个安稳的握手机制。在读出方设置一个专门的发送电路,当此发送电路经过Rd2WrRst宣布了清位信息后,等候写入方经过Wr2RdRst通道送回关于这个信息被接纳的承认。当收到这个信息的承认后,读出方发送电路复位。相同的,写入方也有一个发送电路,操作过程同读出方共同,无非是运用置位信息组。这两个发送电路都各由四个寄存器组成,一位对应一个信元区域。

为了处理Rd2WrRst进入写入方时引起的信号亚稳态,需求在写入方设置一个专门消除亚稳态的电路模块。依据Rd2WrRst和Rd2WrSet特色不相同,这个模块有多种规划办法,可是其主旨都是运用接连两次采样的办法。

这儿介绍一种比较简单的办法。在规划的时分,把Rd2WrRst和Rd2WrSet的信号都规划为电平办法,即当读出方要发送一个信元区域的清位信息的时分,就把Rd2WrRst信号通道里对应的信元区域位设置为‘1’。这个‘1’电平一向坚持到写入方的承认抵达。当这个‘1’电平被写入方采样的时分,因为‘1’同步于读出方的时钟,所以很有或许会发生写入方第一次采样为一个不确切值,即一般意义上的亚稳态状况。可是,因为读出方一向坚持‘1’电平,所以写时钟在第2次采样的时分就会得到一个安稳的采样样本,然后消除了Rd2WrRst的亚稳态。关于处理Wr2RdSet进入读出方的时分引起的信号亚稳态的办法和读出方相同。

关于Rd2WrSet通道里边的信息,其实是读出方给写入方的置位承认。这个信号的源头是写入方宣布的Wr2RdSet,读出方对Wr2RdSet不做任何处理,仅仅单纯地把它里边的信息拷贝到Rd2WrSet通道并回送写入方,当Rd2WrSet进入写入方的时分,进入消除亚稳态电路,最终复位写入方的发送电路。关于Wr2RdRst通道里边的信息操作也和Rd2WrSet的信息相同。整个电路的结构如图所示。

关于信元字节的计数,和一般的办法相同,发生在FIFO的外部,外部的电路需求为FIFO供给依据信元字节计数到信元尾的信息。这个信息用来使得FIFO?的读写地址指针从一个信元区域跳到下一个信元区域。FIFO向外部电路供给FIFO有多少个信元的信息。这个信息加上外部电路自己发生的计数信息,能够知道FIFO是否将满,FIFO是否将空等一系列信息。

经过上面的描绘,能够看到外部电路能够十分自由地操控FIFO的读写地址的改变,这是通用FIFO所不具备的功用。因为FIFO给出的是信元的信息,规划者在做有关UTOPIA协议的电路的时分,能够很方便地运用这个信息。一起,假如规划需求UTOPIA的查错功用,这样的状况更需求外部电路能操控?FIFO的地址改变。然后使得写地址指针回跳以掩盖原先写入的数据。明显,这一功用也是通用FIFO很难完成的。

本文小结

关于这样的FIFO运用还能够延伸到关于非定长包的处理,比如说以太包。因为以太包的特色,要在FPGA中彻底存储一个以太包需求的硬件资源很大,所以,有时分关于以太包的处理都会先把其分为固定长的数据块,并把每一数据块伴以相应的标识以辨认他们是归于哪一个以太包。这样一来,就变成了对固定长数据块的处理。因而,上面所述的FIFO的规划办法又能够用来缓存以太包。