4.3存储空间的分配

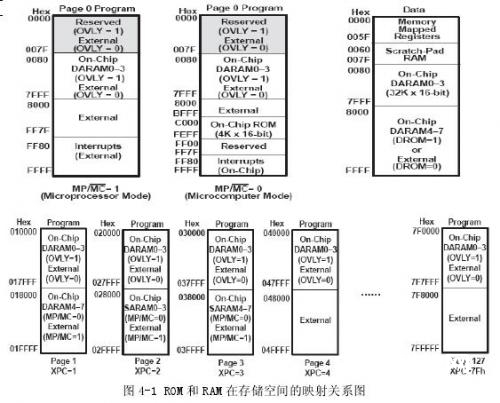

TMS320VC5416的存储空间分为三个部分:程序空间、数据空间、I/O空间。这三个地址空间的总寻址规模为192K.由4.1节的介绍咱们知道TMS320VC5416片内驻有16KW的ROM和128KW的RAM.它们在程序空间和数据空间的映射联系如图4-1.

由图咱们能够看到,当MP/MC=0时,16KW的ROM映射到程序存储空间地址为C000h~FFFFh空间。DARAM0~3驻留在数据空间的0000h~7FFFh.当OVLY=1时,DARAM0~3映射到程序空间每一页的0000h~7FFFh,即拜访程序空间每一页的0000h~7FFFh地址时,适当所以拜访数据空间的DARAM0~3.DARAM4~7驻留在程序空间的018000h~01FFFFh,当DROM=1时,其映射到数据空间地址为8000h~FFFFh空间。程序与数据空间的彼此映射能够削减存储空间之间数据的彼此调用,然后缩短指令的执行时间,进步程序的运转功率。SARAM0~3驻留在程序空间第二页的028000h~02FFFFh,SARAM4~7驻留在程序空间第三页的038000h~03FFFFh.它们都作为程序空间的一部分。

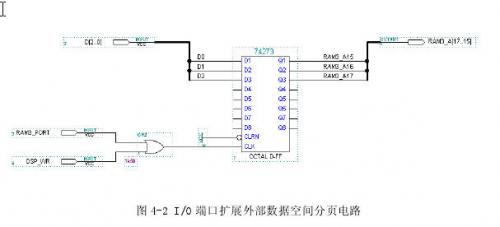

在本项目中,咱们用512K×16Bit的Flash作为DSP的片外程序存储空间扩展,总线16位,用于16位办法的并行引导装载和数据保存。其间既保存了用户主程序、模仿Bootloader等程序,还保存了数据:如中英文字库、DSO波形数据、设置等。别的,咱们还用256K×16Bit的外部RAM作为DSP的片外数据存储空间的扩展。这256K RAM经过I/O扩展(如图4-2)分为8页,每页32K.当要拜访数据存储空间的高32K地址(8000h~FFFFh)时,能够依据RAM3_A[17..15]的值,挑选不同的页去对应数据存储空间的高32K.

在硬件规划中,咱们用VHDL言语编写分配了程序和数据空间地址。部分程序代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ENCODE IS

PORT(DSP_A[22..16]:IN STD_LOGIC_VECTOR(6 DOWNTO 0);

DSP_PS,DSP_DS,A15:IN STD_LOGIC;

FLASH_CS,RAM_CS : OUT STD_LOG%&&&&&%;

);

END ENTITY;

ARCHITECTURE BEHAV OF ENCODE IS

BEGIN

A:PROCESS(DSP_A[22..16],DSP_PS)

BEGIN

IF(DSP_PS=0 ) THEN

IF(DSP_A=0 and A15=1) THEN

FLASH_CS<=0;

ELSIF(DSP_A=8 and A15=0)THEN

FLASH_CS<=0;

ELSIF(DSP_A>8 and DSP_A=15)THEN

FLASH_CS<=0;

ELSE

FLASH_CS<=1;

END IF;

ELSE

FLASH_CS<=1;

END IF;

IF(DSP_DS=0 AND A15=1) THEN

RAM_CS=0;

ELSE

RAM_CS=1;

END IF;

END PROCESS A;

从以上程序以及结合图 4-1,咱们能够得到程序和数据空间的地址分配如表4-2。

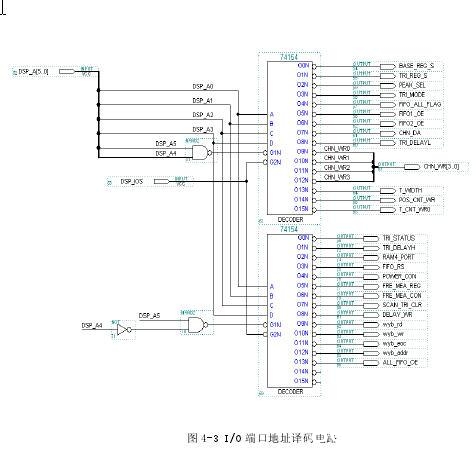

I/O空间也便是I/O端口地址译码,它主要是经过DSP的IOSTRB信号和DSP地址信号的合作译码地址,使之发生相应操作的操控信号。如:时基挑选操控,预触发操控,FIFO读写操控,峰值检测功用挑选等等。它的具体电路完成如图4-3.

第五章显现操控电路

跟着通讯、IT与多媒体商场的鼓起,耗电少、辐射低,易于带着的液晶(LCD)(liquid crystal display)成为手持仪器的首选。与CRT比较,液晶具有以下长处:

◇低功耗。极低的作业电压,只需3-5V,作业电流在几个UA/(cm)*2.因而液晶显现能够和大规模%&&&&&%直接匹配,使便携式电子计算机、电子外表成为可能。

◇平板型结构。液晶显现根本结构是由两片玻璃组成的夹层盒。这种结构的长处,一是在运用上最便利,不管大型,小型,微型都很有用。

◇被迫显现型。液晶显现自身不发光而是靠调制外界光进行显现。

◇显现信息量大。与CRT显现比较,液晶显现没有荫罩约束,像素能够做得很小,这关于未来的高清晰度电视。是个抱负的挑选计划。

◇易于五颜六色化。液晶五颜六色化,十分简略,办法也许多,更可贵的是液晶的五颜六色是能够在色谱上十分精确的复现,因而,不会发生色失真。

◇液晶显现作业时,没有电磁辐射。

◇长寿数。这种器材自身简直没有什么劣化问题。因而寿数极长。

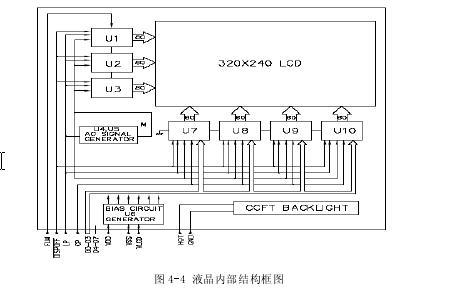

本项目中,咱们选用了NANYA公司型号为LTBHB203E1K的是非显现屏。它是320×240点阵的LCD.内部结构如图4-4所示。

一般LCD显现都选用专用的液晶显现操控模块,完成屏幕切割,屏幕逻辑运算等杂乱的图形功用。但这样有必要要由DSP来操控显现模块,而且其改写频率遭到必定约束。示波表的实时性要求十分高,所以对改写率要求也就很高,而且液晶显现界面根本上仅仅显现结构和实时波形等简略的图形,所以咱们就直接用FPGA发生LCD所需求的各种显现操控时序。

显现操控电路主要由两部分组成,一部分是LCD的时序操控电路,另一部分是显现数据的传输电路。下面咱们就将环绕这两个方面做具体的介绍。

5.1显现时序操控电路

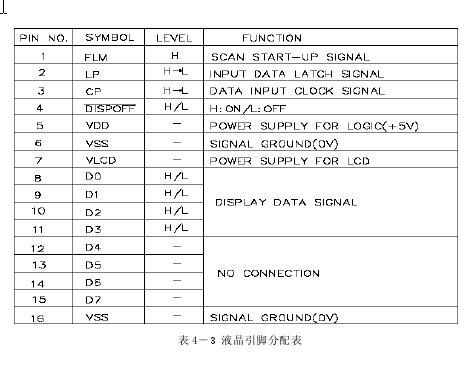

此液晶共有16根对外引脚,其引脚分配表见表4-3,其间有三根信号线,一根操控线,八根数据线。移位脉冲信号CP是指当来一个CP脉冲时,LCD读取数据线上的数据拿去显现。LP信号为行同步信号,即当CP读取完一行的数据后,发生一个LP信号,将数据锁存起来。FLM信号为场同步信号,即每显现完一屏数据发生一个FLM同步信号。D0~D7是显现数据传输信号线,其间D4~D7数据线无效,也便是说一个CP只进D0~D3四位数。DISPOFF操控信号是操控液晶是否显现的,当为1时显现,为0时不显现。

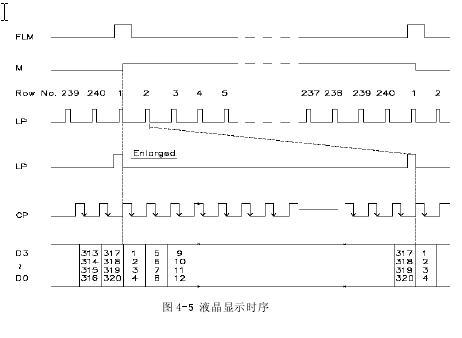

咱们所运用的是320×240点阵是非液晶,每个象素点只由一位数据表明。LCD显现从榜首行开端,每发生一个CP,读取4位数据,这样要显现一行需求320/4=80个CP时钟,而液晶是240行,所以LP的频率是CP的1/80,FLM的频率是LP的1/240.其各时钟信号的时序图如图4-5所示。FLM的频率一般要求在175Hz~185Hz之间,所以咱们在规划时把CP的频率设置在3.1MHz左右。

显现数据在FPGA内传输和DSP内部处理时咱们是按两位表明一个像素点来处理的,当要显现波形的时分,再将这两位数相或后拿去显现。这样做的优点是只需稍稍改动显现数据的输出办法,而不需对硬件和软件做大的改动,该体系就相同能够适用于五颜六色液晶显现屏。