一、概述.

SPI, Serial Perripheral Interface, 串行外围设备接口, 是 Motorola 公司推出的一种同步串行接口技能. SPI 总线在物理上是经过接在外围设备微操控器(PICmicro) 上面的微处理操控单元 (MCU) 上叫作同步串行端口(Synchronous Serial Port) 的模块(Module)来完结的, 它答应 MCU 以全双工的同步串行方法, 与各种外围设备进行高速数据通讯.

SPI 首要应用在 EEPROM, Flash, 实时时钟(RTC), 数模转换器(ADC), 数字信号处理器(DSP) 以及数字信号解码器之间. 它在芯片中只占用四根管脚 (Pin) 用来操控以及数据传输, 节省了芯片的 pin 数目, 一起为 PCB 在布局上节省了空间. 正是出于这种简略易用的特性, 现在越来越多的芯片上都集成了 SPI技能.

二、 特色

1. 选用主-从方法(Master-Slave) 的操控方法

SPI 规则了两个 SPI 设备之间通讯有必要由主设备 (Master) 来操控次设备 (Slave). 一个 Master 设备可以经过供给 Clock 以及对 Slave 设备进行片选 (Slave Select) 来操控多个 Slave 设备, SPI 协议还规则 Slave 设备的 Clock 由 Master 设备经过 SCK 管脚供给给 Slave 设备, Slave 设备自身不能发生或操控 Clock, 没有 Clock 则 Slave 设备不能正常作业.

2. 选用同步方法(Synchronous)传输数据

Master 设备会依据即将交流的数据来发生相应的时钟脉冲(Clock Pulse), 时钟脉冲组成了时钟信号(Clock Signal) , 时钟信号经过时钟极性 (CPOL) 和 时钟相位 (CPHA) 操控着两个 SPI 设备间何时数据交流以及何时对接纳到的数据进行采样, 来确保数据在两个设备之间是同步传输的.

3. 数据交流(Data Exchanges)

SPI 设备间的数据传输之所以又被称为数据交流, 是因为 SPI 协议规则一个 SPI 设备不能在数据通讯进程中仅仅只充任一个 “发送者(Transmitter)” 或许 “接纳者(Receiver)”. 在每个 Clock 周期内, SPI 设备都会发送并接纳一个 bit 巨细的数据, 相当于该设备有一个 bit 巨细的数据被交流了.

一个 Slave 设备要想可以接纳到 Master 发过来的操控信号, 有必要在此之前可以被 Master 设备进行拜访 (Access). 所以, Master 设备有必要首要经过 SS/CS pin 对 Slave 设备进行片选, 把想要拜访的 Slave 设备选上.

在数据传输的进程中,每次接纳到的数据有必要鄙人一次数据传输之前被采样. 假如之前接纳到的数据没有被读取, 那么这些现已接纳完结的数据将有或许会被丢掉,导致 SPI 物理模块终究失效. 因而, 在程序中一般都会在 SPI 传输完数据后, 去读取 SPI 设备里的数据, 即便这些数据(Dummy Data)在咱们的程序里是无用的.

三、 作业机制

1. 概述

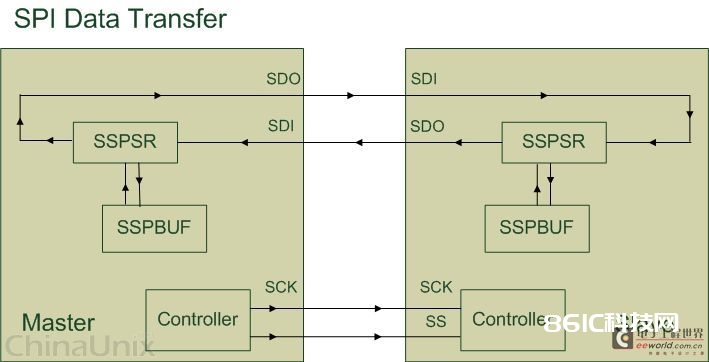

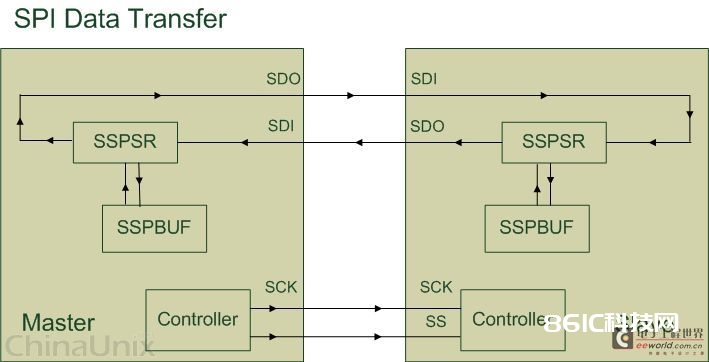

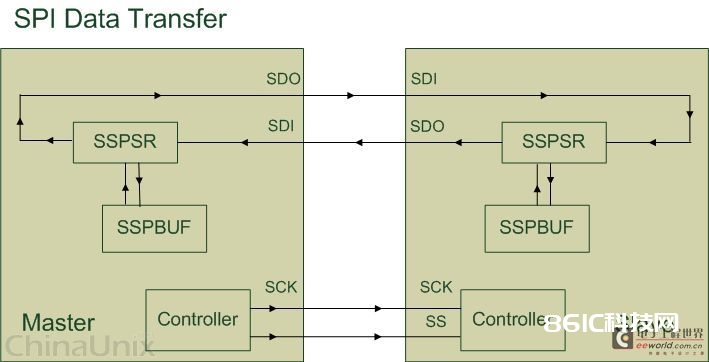

上图仅仅对 SPI 设备间通讯的一个简略的描绘, 下面就来解释一下图中所示的几个组件(Module):

SSPBUF, Synchronous Serial Port Buffer, 泛指 SPI 设备里边的内部缓冲区, 一般在物理上是以 FIFO 的方法, 保存传输进程中的暂时数据;

SSPSR, Synchronous Serial Port Register, 泛指 SPI 设备里边的移位寄存器(Shift Regitser), 它的作用是依据设置好的数据位宽(bit-width) 把数据移入或许移出 SSPBUF;

Controller, 泛指 SPI 设备里边的操控寄存器, 可以经过装备它们来设置 SPI 总线的传输方法.

通常情况下, 咱们只需求对上图所描绘的四个管脚(pin) 进行编程即可操控整个 SPI 设备之间的数据通讯:

SCK, Serial Clock, 首要的作用是 Master 设备往 Slave 设备传输时钟信号, 操控数据交流的机遇以及速率;

SS/CS, Slave Select/Chip Select, 用于 Master 设备片选 Slave 设备, 使被选中的 Slave 设备可以被 Master 设备所拜访;

SDO/MOSI, Serial Data Output/Master Out Slave In, 在 Master 上面也被称为 Tx-Channel, 作为数据的出口, 首要用于 SPI 设备发送数据;

SDI/MISO, Serial Data Input/Master In Slave Out, 在 Master 上面也被称为 Rx-Channel, 作为数据的进口, 首要用于SPI 设备接纳数据;

SPI 设备在进行通讯的进程中, Master 设备和 Slave 设备之间会发生一个数据链路回环(Data Loop), 就像上图所画的那样, 经过 SDO 和 SDI 管脚, SSPSR 操控数据移入移出 SSPBUF, Controller 确认 SPI 总线的通讯方法, SCK 传输时钟信号.

2. Timing.

上图经过 Master 设备与 Slave 设备之间交流1 Byte 数据来阐明 SPI 协议的作业机制.

首要,在这里解释一下两个概念:

CPOL: 时钟极性, 表明 SPI 在空闲时, 时钟信号是高电平仍是低电平. 若 CPOL 被设为 1, 那么该设备在空闲时 SCK 管脚下的时钟信号为高电平. 当 CPOL 被设为 0 时则正好相反.

CPHA: 时钟相位, 表明 SPI 设备是在 SCK 管脚上的时钟信号变为上升沿时触发数据采样, 仍是在时钟信号变为下降沿时触发数据采样. 若 CPHA 被设置为 1, 则 SPI 设备在时钟信号变为下降沿时触发数据采样, 在上升沿时发送数据. 当 CPHA 被设为 0 时也正好相反.

上图里的 “Mode 1, 1” 阐明晰本例所运用的 SPI 数据传输方法被设置成 CPOL = 1, CPHA = 1. 这样, 在一个 Clock 周期内, 每个独自的 SPI 设备都能以全双工(Full-Duplex) 的方法, 一起发送和接纳 1 bit 数据, 即相当于交流了 1 bit 巨细的数据. 假如 SPI 总线的 Channel-Width 被设置成 Byte, 表明 SPI 总线上每次数据传输的最小单位为 Byte, 那么挂载在该 SPI 总线的设备每次数据传输的进程至少需求 8 个 Clock 周期(疏忽设备的物理推迟). 因而, SPI 总线的频率越快, Clock 周期越短, 则 SPI 设备间数据交流的速率就越快.

声明:本文内容来自网络转载或用户投稿,文章版权归原作者和原出处所有。文中观点,不代表本站立场。若有侵权请联系本站删除(kf@86ic.com)https://www.86ic.net/xinpin/jishu/257257.html