摘要:研讨并规划了一种依据SoPC的千兆以太网接口卡,要点对千兆以太网接口卡的组成、作业流程、EMAC、时钟办理、用户逻辑规划和软件规划等关键技能进行了描绘,并依据Xilinx渠道验证了千兆以太网接口卡的有用性。本文的研讨为依据SoPC完结自主化的千兆以太网产品具有必定的工程参考价值。

关键词:千兆以太网;SOPC;接口卡

0 导言

跟着通讯技能的迅猛发展,千兆以太网以其传输速度快、间隔远、接口遍及、成本低、易于集成等特色,遭到业界喜爱,广泛运用在通讯、金融、商业、教育和政府机关等范畴。

SoPC即可编程片上体系,以FPGA为载体结构面向运用的完好体系,具有开发周期短、难度和成本低的长处。Xilinx公司推出依据FPGA器材开发SoPC的开发环境EDK,并在新一代器材中集成硬核EMAC,使得FPGA能够和千兆以太网完结无缝衔接。

本文研讨并规划了一种依据SoPC的千兆以太网接口卡,要点对其组成、作业流程、EMAC、时钟办理、用户逻辑规划和软件规划等关键技能进行了描绘,并开发测验用例进行测验验证。

1 千兆以太网接口卡体系结构

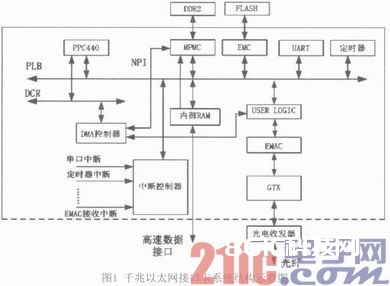

本文选用Xilinx公司的Virtex-5 FX70T作为中心器材,依据嵌入式处理器PPC440完结千兆以太网接口卡高速通讯功用。在规划完结中,所规划的接口卡包括PPC440、DMA操控器、MPMC、EMC、UART、定时器、EMAC、中止操控器和GTX等内容,如图1所示。

其间,PPC440是整个SoPC的中心,它操控一切部件,运转操控程序。Xilinx供给PPC440的硬核,支撑32位流水线,支撑32位运算,单核最高主频550MHz,处理才能1000DMIPS。在本规划中,PPC440作业主频为400MHz,内部PLB总线频率为100MHz。

DMA操控器能够在CPU装备之后长期地独立引导以太网数据在EMAC和MPMC之间高速交流。Xilinx供给独立的IP核CDMAC,CDMAC的结构包括4个DMA引擎,128bytes存储器触发才能,涣散的地址数据Buffer。CDMAC针对MPMC供给了2个独立的数据操作端口,针对EMAC供给了为其硬件总线结构的4个收发端口,在CDMAC内部稀有据通道、操控通道,各包括2个DMA引擎,能够依据数据的长度发生DMA的不同长度读写触发作业形式,最大功率地进步操作功率。

DDR2用来处理FPGA内部RAM缺乏的问题,本体系选用MPMC作为DDR2的操控器。MPMC供给了1~8个端口来存取内存,每个端口都能挑选一系列衔接特性接口模块(PIMs),包括PPC440MC、PLB、NPI、XCL和VFBC等接口。本体系将MPMC装备为两端口形式。一个端口是PPC440MC,用于和

PPC440的接口;另一个端口为NPI接口,数据宽度为64位,用于要发送数据的输入DDR2作为缓存。

FLASH用来固化和储存可执行的软件程序,经过EMC接口衔接在PLB总线上。UART用来完结PC机和SoPC体系之间的通讯,定时器用来为实时操作体系供给周期节拍。

中止操控器接纳FPGA内部各种中止,包括定时器中止、串口中止等,并上报给PPC440,等候PPC440进行处理。

EMAC选用Xilinx供给的硬核完结,用户逻辑完结对EMAC的拜访和操控。EMAC发生的数据经过GTX进行串并/并串转化后,经过外部光纤进行通讯。

2 千兆以太网接口卡规划

千兆以太网接口卡依据SoPC规划,选用Xilinx供给的PPC440、MPMC、EMC、EMAC等软硬核,结合自主开发的用户逻辑,共同完结干兆以太网接口卡的通讯功用。

2.1 作业原理

千兆以太网接口卡发送进程如下:

(1)当需求发送时,经过外部高速接口将传输数据写入内部RAM中,暂时存入DDR2中;

(2)当DDR2中数据到达必定的数量后,向PPC440发送中止信号;

(3)当PPC440收到中止请求后,经过DMA通道将数据从千兆以太网送出。

千兆以太网接口卡接纳进程如下:

(1)当千兆以太网接纳数据后,发生中止;

(2)当PPC440收到中止请求后,经过DMA通道将数据写入DDR2中;

(3)外部高速接口经过内部RAM,将DDR2中的数据读出。

2.2 EMAC

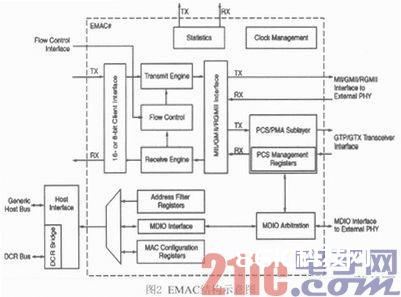

千兆以太网MAC选用Xilinx公司供给的三速嵌入式以太网MAC核(EMAC)完结。该IP核集成了10/100/1000Mb/s以太网MAC核,契合802.3—2002标准,支撑全双工的10/100/10013Mb/s,半双工的10/100Mb/s。支撑多种可装备的物理层接口,包括MII、GMII、RGMII、SGMII和1000BASE—XPCS/PMA接口。EMAC中包括主机接口、客户端、时钟办理、MII/GMII/RGMII接口等,如图2所示。

在规划中,依据体系需求对EMAC进行装备。装备接口为主机装备形式,并以8位数据进行拜访,装备速率为固定千兆形式,装备物理接口为SGMII形式,经过GTX进行串并/并串转化。

2.3 时钟办理

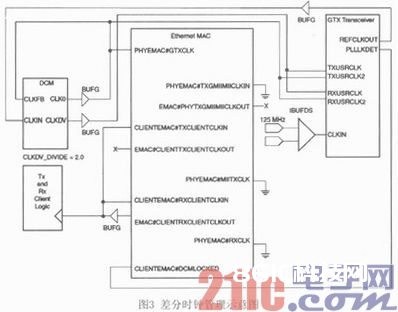

整个体系需求供给2个外部时钟:40MHz单端时钟和125MHz差分时钟。

40MHz时钟经过倍频发生100MHz、200MHz和400MHz时钟。100MHz时钟为PLB总线供给时钟,200MHz时钟为DDR2供给时钟,400MHz时钟为

PPC440内频时钟。

125MHz差分时钟用于供给GTX、EMAC和内部逻辑时钟。125MHz高质量的差分时钟经过IBUFDS后直接衔接GTX的CLKIN端,然后GTX回来一个125MHz时钟REFCLKOUT,经过内部DCM发生125MHz和162.5MHz时钟,别离供给给GTX并行端时钟、EMAC时钟和内部逻辑,如图3所示。

2.4 用户逻辑规划

用户逻辑中完结三个功用:EMAC装备接口规划、客户端发送单元规划和客户端接纳单元规划。

EMAC装备接口完结PPC440和EMAC之间的拜访操控。EMAC经过Xilinx供给的IPIF接口挂接在PLB总线上。

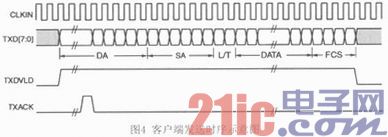

发送单元担任将待发送的数据依照必定时序发送到MAC核,再经过GTX输出到数据链路中。客户端发送时序如图4所示。

客户端发送进程如下:

(1)当客户端需求发送数据时,首先将榜首个字节送到数据线(TXD),一起将数据有用信号(TXDVLD)置高;

(2)当EMAC收到榜首个字节后,回来一个应对信号(TXACK);

(3)客户端收到应对信号后,将剩下数据依照字节发送,在数据发送完结之前,TXDLVD信号一向为高。

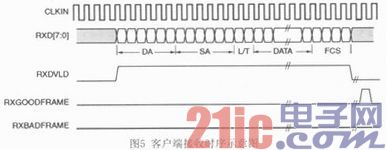

接纳单元担任依据客户端接纳时序接纳来自于MAC的数据。客户端接纳时序如图5所示。

客户端接纳进程如下:

(1)当EMAC稀有据发送到客户端时,接纳数据信号(RXD)和数据有用信号(RXDVLD)一起有用;

(2)接纳单元依据RXD和RXDVLD接纳来自EMAC的数据;

(3)当数据接纳完结后,假如接纳数据正确信号(RXGOODFRAME)有用,标明该帧数据正确,则将数据提交。假如数据过错信号(RXBADFRA ME)有用,标明该帧数据过错,则将数据丢掉。

2.5 软件规划

在规划中,软件担任完结体系的运转、设备的操控、体系各部分功用完结、以太网的TCP/IP协议的完结等功用。运用Xilinx供给的EDK下集成的东西SDK,运用C言语进行编程。

EDK供给第三方支撑库TRECK,它运用一种简化的TCP/IP协议,并向用户供给上层的API函数,完结了一种高效的、便于与SOPC完结的TCP /IP协议。

3 仿真与验证

本论文选用Xilinx Virtex-5 FPGA芯片对千兆以太网接口板进行规划和完结,并选用Modelsim6.5d进行仿真验证,选用ISE12.1进行归纳、布局布线、生成bit文件。

将生成的bit文件下载到自主规划的板卡中,并开发测验用例进行测验、验证。实践测验结果标明:依据SoPC的千兆以太网接口板体系功用正确,传输速率到达了线速。

4 结束语

本文研讨并规划了一种依据SoPC的千兆以太网接口卡,要点对其组成、作业流程、EMAC、时钟办理、用户逻辑规划和软件规划等关键技能进行了描绘,并开发测验用例进行测验验证。经严厉测验验证标明,该千兆以太网接口板功用完全契合体系要求。

本文的研讨对依据SoPC完结自主化的千兆以太网产品具有必定的工程参考价值。