1. 概述

近些年来,各种电路功用,包括模仿电路和数字电路,越来越多地用单片集成电路来完结。选用单片集成电路不只能够有效地进步电路可靠性和其它功用,并且也大大地下降了运用难度。许多单片集成电路的信息输入和作业操控是经过数字信号完结的。常用的操控器材为微操控器和可编程逻辑器材。

因为微操控器一次只能履行一条指令,因而它的首要局限性是作业速度。选用硬件计划规划的数字体系总是比软件计划的数字体系的作业速度快。对数据的传输速率有较高要求的情况下,选用可编程逻辑器材是一种较好的挑选。可编程逻辑器材中的FPGA器材不只供给通用逻辑单元,并且还供给了能够构成各种存储器的嵌入式阵列块。

2. nRF2401A无线收发芯片介绍

无线收发芯片nRF2401是挪威NORDIC SEMICONDUCTOR公司的产品,它把射频收发电路集成在一块芯片上,芯片内部包括频率归纳器、微波功率放大器、信号调制和解调器等部分。操控器材与nRF2401芯片之间的数字传输经过串行同步接口完结。nRF2401芯片作为一种单片无线收发芯片,它的射频规模为2.4GHz~2.5GHz,这个频率规模被称作为工业—科学—医疗(Industrial-Scientific-Medical,ISM)频带,能够自在运用。

在正常作业形式下,发送端的nRF2401无线收发芯片能够从操控器材接纳数据,然后发射频移键控(FSK)信号;在接纳端nRF2401无线收发芯片接纳频移键控信号,然后把解调发生的数据送到操控器材。正常作业形式具有2种作业办法:ShockBurstTM办法和直接办法。

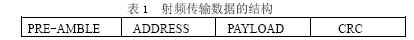

ShockBurstTM办法运用片内FIFO存储器,然后使得操控器材与nRF2401芯片之间的数字传输能够选用较低的数据率,nRF2401芯片之间的数字无线电通信选用较高的数据率。这个长处下降了射频功率器材的作业时刻,因而下降了电源的功耗,这在运用电池供电的场合十分重要。除此之外,ShockBurstTM办法对射频传输数据帧的处理也比较简略。射频传输数据帧包括4个部分,它的结构如表1所示。这个结构关于2种作业办法,ShockBurstTM办法和直接办法,都是相同的。

PRE-AMBLE被称为为前置代码,这个部分的宽度为8位。当作业在ShockBurstTM办法,发射芯片在发送数据时主动把这个部分添加到射频传输数据帧中;接纳芯片从接纳到的射频传输数据帧中主动取掉这个部分。

ADDRESS为用于接纳的nRF2401无线收发芯片的地址,这个部分的最大宽度为40位。当作业在ShockBurstTM办法,发射芯片在发送数据时,操控器材向nRF2401无线收发芯片传送的数据中有必要包括这个部分;接纳芯片从接纳到的射频传输数据帧中将主动取掉这个部分。

PAYLOAD为实践需求传输的信息。当作业在ShockBurstTM办法,这个部分包括的数据位数能够由下面公式核算。

PAYLOAD = 256 – ADDRESS – CRC

CRC为循环冗余查看,这个部分的宽度能够为8位或许16位。循环冗余查看功用只能在ShockBurstTM作业办法下运用,在直接作业办法下不能运用这个功用。发射芯片在发送数据时主动把这个部分加到射频传输数据帧中,它的宽度由芯片的装备字来决议;接纳芯片从接纳到的射频传输数据帧中主动取掉这个部分。

射频传输数据帧中包括较长的地址位和循环冗余查看位尽管减少了实践需求传输的信息运用的数据宽度,可是能够下降误码的发生概率。

3. 数字紧缩的完结

在选用16位接纳地址和16位CRC编码,可用于传输遥测数据的位数可由上式核算出,其数值为224位。为确保待传输的丈量信息具有满足的动态规模,遥测体系的一切模仿/数字转化都选用12位的模仿/数字转化器。运用无线收发芯片nRF2401传输12位的PCM编码,一次只能传输18路丈量信号。

关于监测的模仿信号,小振幅信号比大振幅信号呈现的可能性大,因而选用非线性编码能够用较少的数据位数取得需求的精度,即小振幅信号运用较多的编码,大振幅信号运用较少的编码。这样的非线性编码体系也被称作为紧缩扩展体系,数据在传输之前先被紧缩,然后在接纳端再被扩展。

μ律紧缩扩展是一种常用的算法,它的紧缩特性为:

![]()

式中,Vmax:最大未紧缩模仿输入信号起伏;Vin:当时模仿输入信号起伏;μ:界说紧缩量的参数;Vout:紧缩模仿输出信号起伏。μ值越高,紧缩量越大,μ值为0时,特性为直线,这时无紧缩。

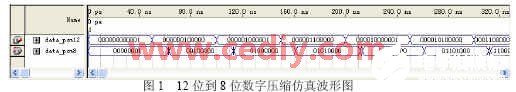

数字紧缩把12位线性编码转化成8位非线性编码,这样在相同的一帧224位丈量数据就能够包容28路信号,比线性编码多出10路。这儿转化的进程是运用8个直线段来近似μ值为255的模仿紧缩特性,每个直线段的斜率等于前一段的二分之一。

8位紧缩码由3段标识码和5位起伏码组成。表2给出12位到8位数字紧缩和扩展编码。12位线性编码中标为X的位在紧缩时被丢掉,标为A、B、C、D和E的位被原样传输。在段0和段1,数据没有被紧缩,原始的12位线性编码能够被完整地康复;在段2,紧缩比为2:1,64个线性编码只生成32个紧缩编码;在段3,紧缩比为4:1,128个线性编码只生成32个紧缩编码。顺次类推,在段7,紧缩比为64:1,2048个线性编码只生成32个紧缩编码。

选用查表的办法是一种常用的编码办法,可是关于表2所示的紧缩编码,运用硬件描绘言语愈加简略,编码速度更快、也节约可编程逻辑器材的资源。运用VHDL的并行条件信号赋值句子完结紧缩编码的代码如下,data_pcm12为12位线性编码,data_pcm8为8位紧缩编码。图1给出运用ALTERA公司的EP1C3T100I7芯片的仿真波形图,完结一次紧缩编码只需求不到15ns的时刻。

data_pcm8 《= “000” & data_pcm12(4 DOWNTO 0) WHEN data_pcm12 《“000000100000” ELSE

“001” & data_pcm12(4 DOWNTO 0) WHEN data_pcm12 《“000001000000” ELSE

“010” & data_pcm12(5 DOWNTO 1) WHEN data_pcm12 《“000010000000” ELSE

“011” & data_pcm12(6 DOWNTO 2) WHEN data_pcm12 《“000100000000” ELSE

“100” & data_pcm12(7 DOWNTO 3) WHEN data_pcm12 《“001000000000” ELSE

“101” & data_pcm12(8 DOWNTO 4) WHEN data_pcm12 《“010000000000” ELSE

“110” & data_pcm12(9 DOWNTO 5) WHEN data_pcm12 《“100000000000” ELSE

“111” & data_pcm12(10 DOWNTO 6);

4. nRF2401A无线收发芯片数据接口的规划

无线收发芯片nRF2401的ShockBurstTM作业办法能够使得操控器材与该芯片之间的数字传输能够选用较低的数据率,以下降对操控器材的要求;nRF2401芯片之间的数字无线电通信选用较高的数据率,最高为1Mbps,以下降电源的功耗。因为无线收发芯片nRF2401从操控器材获取数据和发射频移键控信号是分时进行的,因而操控器材较低的作业速度将下降实践的数据传输速率。

nRF2401芯片的最高数据传输速率也为1Mbps,因为数据格局的非标准,假如选用微操控器完结则只能选用位寻址指令来完结,多条指令才干完结一位数据的传送,使得到达较高的数据传输速率十分困难。运用FPGA器材完结需求的串行同步接口十分便利,运用2MHz的时钟,第一个时钟用于预备数据,第二个时钟用于发生同步时钟,即可取得1Mbps的数据传输速率。

选用有限状况机(FSM)的时序电路模型,运用VHDL完结的nRF2401A无线收发芯片数据接口代码格局如下:

IF (data_read = ‘0’) THEN

current_state 《= 0;

ELSIF (data_read = ‘1’) THEN

IF (clk_sys‘EVENT AND clk_sys = ’1‘) THEN

CASE current_state IS

••••••

WHEN 83 =》

current_state 《= 84;

ce_read 《= ’1‘; data_addr 《= “00000”;

ce 《= ’1‘; clk1 《= ’0‘; data 《= pcm8_m(199); WHEN 84 =》

current_state 《= 85;

ce_read 《= ’1‘; data_addr 《= “00000”;

ce 《= ’1‘; clk1 《= ’1‘; data 《= pcm8_m(199);

••••••

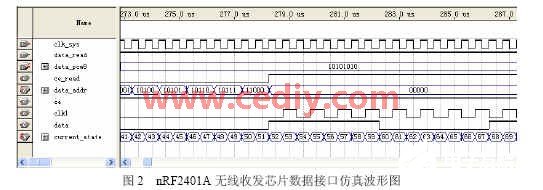

图2是完结的nRF2401A无线收发芯片数据接口代码模块的仿真波形图。遥测体系完结一切模仿/数字转化器输出数字信号的读取,并把这些12位的数据紧缩为8位数据存入一个双口RAM,接着发生一个读数信号data_read。在读数信号低电平期间有限状况机状况信号current_state清零,低电平往后,在时钟信号clk_sys操控下完结nRF2401A的数据接口要求的时序。

在状况机履行进程中,首要发生双口RAM的读使能信号ce_read和地址信号data_addr,把数据转存在一个具有200位的信号pcm8_m中;接着逐位向nRF2401A无线收发芯片传输16位地址和信号pcm8_m中包括的200位数据。完结一切信息的传送今后,状况机停在最终一个状况,等候下一个低电平的读数信号data_read。

5. 总结

本文作者立异点: 运用nRF2401A无线收发芯片使得人工从现场获取数据改变为遥测获取数据,使用FPGA器材取得要求的数据传输速率。运用ALTERA公司的FPGA器材EP1C3T100I7完结nRF2401A的数据接口占用了其2910个逻辑单元的358个(12%),器材还有满足的资源完结模仿/数字转化器的操控以及整个遥测体系的操控。EP1C3T100I7内部的嵌入式阵列块具有59904位,这些资源能够用于完结双口RAM。

责任编辑:gt