45nm铜工艺 面对的应战

摘要:本文总述了铜工艺行将面对的各种改动,包含分散阻障层(barrier)、电镀添加剂、掩盖层以及与多孔超低k电介质之间的整合等。

跟着半导体向45nm工艺的深入展开,铜工艺技能不可避免地要发作一些改动。TaN分散阻障层物理气相堆积(PVD)技能或许将被原子层堆积(atomic layer deposiTIon,ALD)技能所替代,之后或许还会引入钌阻障层技能。钌阻障层技能不再需求电镀种子层,可是其展开情况将取决于研讨成果的展开程度。

电镀槽中的有机“添加剂”也或许会有所改动,由于有些添加剂终究会被包埋在铜中。虽然有机添加剂的运用可以使堆积得到的铜填充没有任何缝隙,一起在密布区不会发作堆积过度的情况,因而不会给CMP带来额定负担,然后减小了CMP难度,可是包埋在铜里的杂质会进步电阻系数,并且使铜在退火时不太简略构成大金属颗粒。

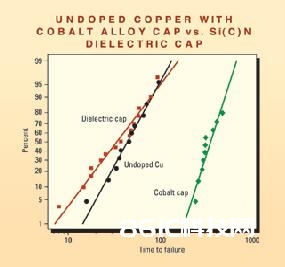

铜工艺也有电致搬迁这个严峻的牢靠性问题,它一般发作在铜导线顶部与电介质相接的交界处。或许的处理办法是在铜外表挑选性地堆积上一层钴钨磷化物(cobalt tungsten phosphide,CoWP)或钴钨硼化物(cobalt tungsten boride,CoWB),终究替代Si(C)N掩盖层,使铜原子搬迁受到限制。

金属颗粒鸿沟、缺点和外表构成的电子散射问题也会逐步突显出来,由于导线尺度很小时电子散射效应会使电阻升高。处理办法包含增大金属颗粒、削减缺点数量和添加金属外表润滑度等。

当然,咱们还需求将铜和多孔超低k介电资料整合在一起,该需求会进一步添加铜工艺的复杂度。其间一个问题是这些多孔资料需求一些孔洞密封工艺,人们对其与堆积在上面的分散阻妨碍层之间的彼此作用感到忧虑,不知道两者之间是否可以彼此兼容。

铜工艺根底

自1990年代中期IBM、Intel、AMD和其他IC制作商决议用铜制工艺替代铝工艺以来,铜工艺的首要长处根本坚持不变。铜电阻较小,具有更好的导电性,这意味着内衔接导线在具有平等乃至更强电流承载才能的一起可以做得更小、更密布。此外,还可以将铜导线做得更薄,然后减小相邻导线之间的相互搅扰。低电阻还意味着可以进步芯片速度,由于RC时间推迟中的R因子变小了。当然,减小RC推迟的C因子也可以进步速度,这便是为什么咱们对低k电介质感兴趣的原因。

VLSI Research Inc.总裁Dan Hutcheson以为,虽然由于前期铜工艺遇到的牢靠性等问题给一些人构成了“铜工艺是十分扎手的工艺”的成见,可是现在世界上简直每个出产130 nm逻辑器材的公司都在运用铜工艺。人们对铜工艺的了解现已十分透彻,并且良品率也很高,有些情况下乃至比相应的铝工艺还要高。另一方面,当半导体公司向65nm和45nm工艺跨进时,铜制作工艺在某些方面明显需求进一步改进,包含分散阻障层堆积办法、掩盖层类型等。虽然超低k电介质的运用被推迟了,可是人们估量那时也将开端运用超低k资料。这意味着将会呈现许多新资料。令人忧虑的是,或许到时候会呈现一些未能预见的牢靠性问题,这些问题一般发作在性质不相似的资料界面。

值得一提的是,铝制程没有走到止境。相反,它依然是许多器材所选用的资料。其间最杰出的是DRAM,它只要很少几层内衔接导线,运转速度也比逻辑器材慢。依据Hynix Semiconductor公司Hyunchul Sohn的资料显现,DRAM制作商还会继续在铝制程上获得一些先进技能,包含铝ALD和CVD技能。Sohn说,虽然总有一天铜制程的制形本钱会比铝还廉价,可是看起来短时间内还不太或许呈现这种情况。

铜工艺与铝工艺彻底不同。铝工艺一般是首要将铝堆积成金属薄膜,蚀刻后再堆积上绝缘的电介质(其间触及金属导线之间高纵宽比空隙的填充);而铜工艺是选用嵌入式工艺(damascene processing)得到图形化的导线的。该工艺得名于源自Damascus陈旧的金属镶嵌技能。上基层铜导线之间经过微通孔(via)相互衔接。为了得到这些微通孔,还需求别的一层光刻和蚀刻进程,因而又称为双嵌入式工艺(dual-damascene)。

双嵌入式工艺中,首要要堆积一层电介质,然后经过两道光刻和蚀刻(或许还需求硬掩膜工艺)在电介质中蚀刻出微通孔和导线沟道结构。由于铜的分散速度很快,很简略在电介质内部移动使器材“中毒”,因而紧接着要堆积一层分散阻障层;然后堆积上一层铜电镀种子层,种子层是铜电镀堆积反响(一般又称为“铜填充”)的必要条件。接着进行退火和平整化处理。对铜进行平整化处理和清洗后,再堆积上一层Si3N4或SiC介电资料层。至此,该工艺周期完毕,然后开端重复下一个工艺周期。 其间,Si3N4或SiC起到后续微通孔(via)蚀刻硬掩膜层的作用。当微通孔与基层金属导线未能很好对齐时,硬掩膜层可以避免蚀刻到基层金属导线的侧边。

铜导线的有用横截面积

当半导体向65 nm和45 nm及以下工艺展开时,铜工艺的首要问题是怎么确保铜导线的电流承载才能不会变差。依据世界半导体技能蓝图(InternaTIonal Technology Roadmap for Semiconductor,ITRS)的界说,导体有用电阻率的“幻数(magic number)”为2.2uΩ-cm。跟着导线线宽的不断微缩,完结该规范的难度开端逐步添加。原因有两个:首要,当导线尺度挨近铜的电子自在程(39.3 nm)时,电子散射问题开端杰出。ITRS指出,“导线和微通孔侧壁粗糙度、多孔低k电介质与侧壁间界面结构、分散阻障层粗糙度和铜外表粗糙度都会给铜导线的电子散射效应构成负面影响,使电阻率增大。这些要素终究会迫使人们选用其它内衔接办法,例如RF或光波波导来替代铜工艺,但那是几年今后的作业。现在,研讨的要点是怎么得到大金属颗粒和使外表尽或许润滑。

还有一个令人忧虑并且火烧眉毛的问题是当导线进一步微缩时经过PVD工艺堆积的铜分散阻障层不能进一步变薄。Applied Materials公司Maydan技能中心总司理John T.C. Lee指出,“相关于铜导线,阻障层横截面积占整个导线横截面积的份额变得越来越大。可是,实践上只要铜才是真实的电流导体。”例如,65nm工艺时,铜导线的宽度和高度分别为~900A和1500A,两恻则分别为100A。这意味着横截面为13500 nm2的导线中实践上只要8400 nm2可用于导电。“它严峻影响了导线的有用阻值。”Novellus Systems整合与先进技能研发部CTO兼履行副总裁Wilbert van den Hoek说。如图1所示,Intel 90 nm铜工艺中分散阻障层占了内衔接导线横截面积的~15%。

图1. Intel 90 nm铜内衔接工艺SEM相片,垫层薄膜占了整个内衔接导线横截面积的~15%。(资料来历:Intel)

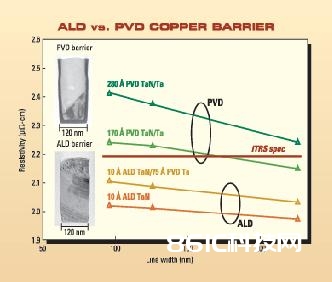

处理办法是选用更薄的铜阻障层,其间最好的办法是选用ALD技能堆积阻障层。有关这项技能的研讨作业现已展开了好几年,并且最近开端呈现商品化设备。Lee说:“咱们的研讨作业获得了很大展开,现已挨近可用于实践出产的水平。”图2显现了为什么选用ALD阻障层时电阻率比选用PVD阻障层更低的原因.

图2. 与PVD阻障层比较,ALD阻障层可以下降导线电阻。到2018年时,ITRS一定会提出2.2 uW-cm的新要求。(资料来历:Applied Materials)

ALD TaN是研讨要点。ALD TaN的原料与现在运用的PVD TaN薄膜根本相同。可是,PVD TaN实践上是氮掺杂的Ta,其组成为TaN0.5,电阻率小于200 uΩ-cm,ALD TaN的组成才真实是TaN。TaN之所以能起到分散阻障层的作用是由于它具有高含氮量和无定形结构。可是,TaN堆积时一般选用有机金属前体,因而残留在薄膜内部的碳也是一个问题。依据所用前体的不同,含碳量散布规模为2 at%到10 at%。当含碳量为~10 at%时,膜的组成为TaN0.9C0.1,电阻率高达1uΩ-cm,以至于不能被人们承受。van den Hoek说:“运用有机金属前体时很难彻底去除碳杂质。可是,你可以选用一些特别办法故意在TaN膜里掺入很多的碳,得到氮掺杂的碳化钽(TaC0.4N0.6),其电阻率为~250 uΩ-cm。”用于铜阻障层ALD堆积的有机金属前体有好几种,例如TBTDET (tert-buthylimidotrisdiethyl- amidotantalum)。 从整合的观念来看,ALD TaN是最直接和最简略的办法,由于它触及到的资料改动是最少的。Lee评论说,“ALD TaN薄膜的试验成果显现它能有用减小导线电阻。现在正在进行的作业是对工艺整合进行认证,使其到达牢靠性的要求。”

用钌处理阻障层和种子层的一切问题?

经过PVD工艺堆积铜电镀种子层时很有意思:首要,种子层有必要满意薄,这样才可以避免在高纵宽比结构上堆积铜时呈现顶部外悬结构,避免发作空泛;可是它又不能太薄。

现在正在评价的一个处理办法是将铜直接镀在分散阻障层上。其间,尤其是用钌作为阻障层具有很好的远景。钌不只有或许替代分散阻障层常用的Ta/TaN两步工艺,并且还能一起替代电镀种子层。由于钌是导体,因而铜可以直接电镀在上面。van den Hoek介绍说:“钌是令人十分感兴趣的资料,由于它是一种准贵金属。钌不简略被氧化,可是即便被氧化了,生成的氧化钌也是导体。”钌的别的一个优点是它可以在规范电镀液中进行铜电镀反响。“选用现有电镀液在钌上电镀时,其体现与在铜上面电镀时彻底相同。”

可是,依据Lee的观念,现在还存在一些问题需求处理。用~100A钌替代~1200A铜种子层时,由于厚度和电阻率的改动,种子层外表电阻进步了~100倍。此外,还需求从头认证电镀均匀性和成核特性。他说:“器材牢靠性很大程度上取决于界面性质和质量。为了到达SM和EM的严厉要求,还需求对钌堆积膜的成分、形状、附着性等进行进一步优化。”

65 nm以下工艺时,在很薄的种子层上进行铜电镀会呈现一些要害性问题。Applied Maeterials公司平整化和电镀产品部副总裁兼总司理Russell Ellwanger说:“咱们发现电镀刚开端时的几秒钟可以决议是否可以成功地完结整个铜电镀进程。经过晶片浸入视点的操控使种子层被均匀潮湿是十分重要的一步,它能消除浸入进程中发作的一些缺点或是被吸附在上面的细小气泡。相同,晶片上的缺点情况也变得十分重要。铜电镀工艺发作的某些缺点,特别是电镀刚开端几秒钟内构成的缺点,在后续平整化工艺中是不能(或很难)被磨掉的,终究会影响产品良品率。”

至于用一层钌薄膜一起替代分散阻障层和电镀种子层的想象依然存在一些问题。van den Hoek说:“从前有段时间内人们期望钌的阻障作用可以满意满意要求,可是现在大部分人得出的结论是很薄的钌堆积层或许起不到满意的阻挠分散作用。”相反,他以为处理办法应该是先用ALD工艺堆积一层很薄的分散阻障层,然后用ALD工艺堆积钌作为阻障层和种子层。“可是,你要设法将整个叠层结构的厚度操控在50A~70A以内,然后减小导线电阻的影响。

处理种子层内呈现孔洞的别的一个处理方案是用无电极电镀技能对这些缺点进行修补。该技能又称为种子层增强技能(seed layer enhancement或简称SLE)。成果得到了十分完美的铜填充相片。可是也有人对修补层与底下阻障层之间的附着性提出了疑问,忧虑在一些薄缺点会引起电致搬迁孔洞和电路失效问题。

按捺、促进和平整化试剂

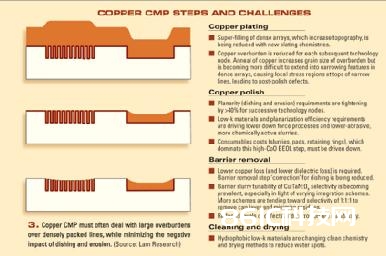

电镀工艺的首要意图是在晶片上镀上一层细密、无孔洞、无缝隙和其它缺点、散布均匀的铜。此外,它还有其它一些要求,例如在对大尺度、空阔区结构进行填充的一起,可以对密布区、高纵宽比结构和微通孔等进行填充。当然,咱们还期望电镀后外表可以尽或许平整,削减后续CMP工艺的问题,其间最明显的是凹坑和腐蚀问题(图3)。Ellwanger说:“由于填充体现很大程度上取决于电镀液的化学反响,因而坚持每片晶片电镀时化学环境的稳定性十分重要。可是,在电镀工艺进程中有机添加剂会不断分化并且在电镀槽中不断累积。因而,削减添加剂分化、坚持电镀液成分不变是十分要害的要素。”

图3. 铜CMP要处理导线密布区CMP负担过重的问题,一起还要尽或许减小凹坑(dishing)和腐蚀(erosion)带来的负面影响。(资料来历:Lam Research)

铜电镀液一般由硫酸铜(CuSO4)、硫酸和水组成,呈淡蓝色。抱负的填充进程首要是铜均匀地堆积在侧壁和底部,然后快速切换为从底部向上填充,避免发作缝隙和孔洞。为了完结上述作用需求运用两种有机添加剂:按捺剂和促进剂。当晶片被浸入电镀槽时,首要进行的是均匀性填充。填充反响动力学受按捺剂操控。接着,当促进剂到达临界浓度时,电镀开端从均匀性填充转变成由底部向上的填充进程。促进剂是一种聚合物/氯化物混合物,它会吸附在铜外表,下降电镀反响电化学反响势,促进快速堆积反响。

问题是填充进程完结后促进剂不能主动中止作用,而是漂浮在铜外表继续促进铜堆积反响。由于狭隘、密布结构的填充速度比宽广、空阔结构快,因而会引起密布区过度电镀,给CMP带来额定负担的问题。处理办法是添加第三种添加剂:引起促进剂分化反响的平整化试剂。这种添加剂的运用作用很好,仅有的问题是与促进剂不同它会被包埋在铜里边。van den Hoek说:“为了处理过度电镀的问题,咱们运用了较高浓度的平整化试剂,可是其缺点是加剧了铜污染。”好消息是人们现已找到了新的平整化试剂,它可以起到相同的作用可是不会被掺杂在铜里边。

“为了满意不断呈现的新要求,例如对300 mm衬底进行潮湿、对越来越小的微通孔进行填充、不断进步纯度、为45 nm工艺供给无孔洞和无缺点电镀等,咱们有必要继续改进有机促进剂、按捺剂和平整化试剂的各个单项功能体现,并在三者之间相互平衡,终究到达更好的归纳功能。”Rohm和Haas电子资料公司微电子技能部EP-Cu商场司理Mike Rousseau说。“130 nm和90 nm工艺的添加剂组合不能到达这些愈加严厉的要求和方针。”

电致搬迁问题的处理办法:挑选性CoWP

人们从前以为铜具有比铝更好的抗电致搬迁才能。可是,当铜制程呈现今后,成果恰恰相反,至少关于小尺度结构来说是这样的。

铜的电致搬迁是一种外体现象,发作在铜原子可以自在移动的当地(一般是铜和其它资料之间附着性较差的界面处)。在现在的双嵌入式结构中,电致搬迁最常发作的当地是铜导线上部与SiC等电介质层相交代的当地。Lee指出,“假如你未能正确处理这些界面,那么它将是一个薄缺点。这个薄缺点会引起链式反响,铜原子移走后忽然构成一个孔洞,构成电致搬迁失效。与铝不铜,铜导线越小越细,问题越大。

处理办法之一是对铜外表进行处理,改进铜与SiC之间的附着性。一般该办法会用到SiC堆积工艺中的硅甲烷(Silane)。硅甲烷不简略受操控,由于它会穿透到铜里边,使电阻率变大。别的一个办法是在铜外表上挑选性地堆积一层含钴的薄膜,一般是CoWP或CoWB。该办法作用很好,抗电致搬迁才能可以进步10倍以上。可是该工艺依然存在一些问题有待处理:

1)外表平整度被改动了,除非CMP后先对铜进行recess处理;

2)多了额定一步工艺,添加了本钱;

3)这是一道挑选性工艺,特别情况下或许会比较扎手,例如当有些铜残留物留在电介质空阔区时。

“用CoWP对铜外表进行掩盖的试验成果显现器材牢靠性得到了改进,并且还能进步65 nm器材的功能(CoWP掩盖层的添加可以明显进步电流密度)。IC制作商期望可以在45 nm工艺时取消蚀刻中止层,下降有用介电常数k值。”堆积溶液供货商Blue29公司CTO Igor Ivanov说。

图4. 铜的电致搬迁数据显现在铜外表堆积一层钴掩盖层后,牢靠性比传统Si(C)N掩盖工艺进步了10倍。