人类获取的信息中70%来自于视觉。视频信息具有直观性、确切性和高效性等长处,其在多媒体信息中占有重要位置,成为了主导现代生活的主力军。可是,视频信息信息量太大,对信息存储设备及通讯网络均提出了很高要求,严峻阻止了人们对有用信息的获取和运用。而处理这个问题的途径便是视频编码即视频压缩。

现在,视频编码的主操控芯片主要有3种:ASIC、FPGA和DSP。ASIC和PGA归于硬件规划,DSP归于软件规划。从功用上说,全定制ASIC(Applieation Speeifie IntegratedCircuit)的功耗低、规划密度大并且能够完结高速规划,但一起其开发周期很长,投片本钱很高并且不容易对处理计划进行优化,运用规模很窄;DSp(Digital Signal Proeessing)能够供给强壮的数字信号处理才能,其可编程特征能够支撑各种规范格局的视频编解码算法,但其处理速度低、硬件结构不灵敏;FPGA(Field Programmable Gato Airay)兼有了两者的一些长处如可编程、功耗低一级,一起又具有规划周期短、开发本钱低、处理速度快、规划灵敏等特色。

1、 运动估量原理

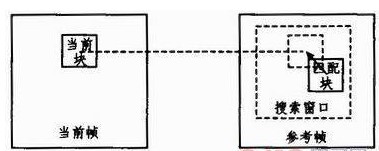

运动估量主要是针对帧间猜测,去除视频帧在空间域和时刻域的冗余度。块匹配办法是现在编码功率较高,遍及选用的一种编码办法。首要,其要将当时帧进行区分。长期实践标明,将当时帧区分为多个16×16的块是比较合理的。其次,要根据区分出的当时块的具体情况,以及所选用的查找办法来决议查找窗口的巨细。最终,要在所确认的查找窗口里边,根据某种块匹配原则找到当时块的匹配块以及由匹配块到

当时块的运动矢量。图1所示是块匹配法的原理框图,其间的箭头便是由参阅帧到当时帧的运动矢量。

现在常常选用的块匹配原则主要有归一化互相关函数(NCCF),最小均方差(MSE)以及最小绝对值(MAD)。其间因为SAD原则在算法上并不需要做任何的乘法运算,能够削减许多的时刻资源和硬件资源,然后使得SAD原则成为了现在一般运用的匹配原则。

![]()

其间A是参阅帧中的查找窗口区域,k-1和fk别离是当时帧和参阅帧中的像素点值,(x0,y0)是块中的其间一个点。[page]

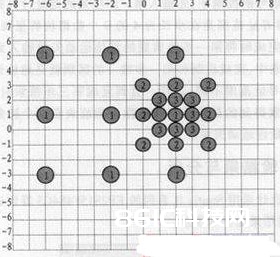

查找选用的是三步查找法,它是依照由粗到细的查找理念,以一个像素为查找精度,分为4,2,1,3个查找步长进行查找。一般选取原点作为起始点,别离依照4,2,1,3个步长组成9个点构成的点群进行匹配运算,每次都是以差错最小的块为准匹配块,在第二和第三步查找时别离以第一和第二步查找到的准匹配块作为它们查找的起始点。原理如图2所示。

2、 硬件完结

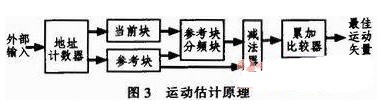

运动估量的原理图如图3所示。

2.1 地址计数器模块

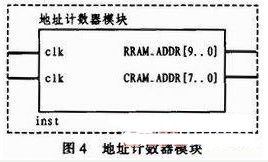

地址计数器主要是发生出能够在RRAM(参阅块存储器)和CRAM(当时块存储器)中有意图地进行寻址的地址信号。如图4所示。

地址计数器模块的规划与当时块和参阅块的存储有很大的联系。将数据存入当时块存储器和参阅块存储器时的次序是由左到右,由下到上,即当时块存储器是(-7,-7),(-6,-7),(-5,-7)……(8,-7),(-7,-6),(-6,-6)……(8,7),(8,8)。而参阅块存储器是(-15,-15),(-15,-14),(-15,-13)……(-15,16),(-14,-15),(-14,-14)……(16,15),(16,16)。则可知在寻址当时块存储器时能够直接依照地址的由左到右,由下到上累加。其核算公式如式(2)所示:

C_addr=(j+7)×16+(i+8) (2)

关于参阅块存储器,它是一个32×32的数据块,规划的意图是从其间取出契合三步查找法的9个数据块,当然这九个数据块都是16×16的,并且是以原点为中心组成的查找点群。其核算公式如式(3)所示:

R_addr=(j+15)x32+(i+16) (3)

Clk是时钟频率信号,当它发生上升沿跳变时会使得发生的地址跳变到下一个新值。

Clr是清零信号,当它是低电平时,地址计数器能够发生从零开端的接连地址。

因为,当时块存储器只是一个16×16的RAM,其总的存储空间是256,则可知运用八位地址就能够进行寻址整个空间,即CRAM_ADDR是八位输出信号。而参阅块存储器是一个32×32的的RAM,其总的存储空间是1 024,则可知运用十位地址就能够进行寻址整个空间,即RRAM_ADDR是十位输出信号。

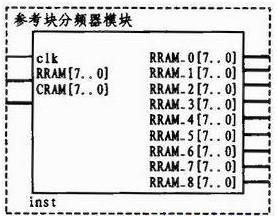

2.2 参阅块分频器模块

参阅块分频器模块主要是将从参阅块存储器中输出的信号经过分频处理后,存储在9个独立的单元,以便后续的处理,如图5所示。

由参阅块输出的信号是256×9个接连的像素值,而当时块输出的信号只是256个接连信号在接连时钟驱动下的九次重复,这样就很难在256×9个时钟周期内完结对9个匹配块的处理,更难在256个时钟周期内完结。因而要经过参阅块分频器将参阅块存储器接连输出的256×9个像素点值进行九次分频,存储在9个RAM单元之中。这样当下一个时钟周期的上升沿到来时,这9个RAM能够一起输出信号,并在接下来的255个时钟周期之后将里边存储的一切信号输出,并且输出的这些信号彼此之间是彻底独立的。一起,为了使后边的各模块能够很好的进行,参阅块分频器模块还引进了当时块的像素值信号,使得存入9个RAM单元的信号不只是是参阅块的像素点值,还有当时块的像素点值以便确保后边的减法器能够正常作业。

2.3 减法器模块

减法器模块主要是完结当时块像素点值和参阅块像素点值之间的作差,并将做差成果进行取绝对值运算。本减法器是选用9个LPM(参数化模块库)元件库中的减法器组成的。而LPM中的减法器将被减数和减数明确地分隔了。因而,在将当时块和参阅块像素点值输入到减法器之前先对二者进行比较,再别离输入到减法器的被减数和减数端口。这样当减法器设置为无符号数运算时,输出成果就相当于取了绝对值的差

值。从时钟周期的视点发现,整个减法器在256×9个时钟周期内是都在运转的,可是所要收集的有用信号只是是9个独立的256个时钟周期,即每个减法器只是运用256个时钟周期的有用信号,其他时钟周期内的信号关于其他减法器是有用信号,可是关于本减法器却是搅扰信号,必需要消除。这便是在参阅块分频器里边引进当时块信息的原因。

2.4 累加比较器模块

累加比较器主要是完结对每个减法器输出的取过绝对值的差值信号的累加,并将累加成果进行比较输出最佳运动矢量。累加比较器的规划和减法器的规划有很大联系,除了在上述的取绝对值方面二者彼此要求比较严厉之外,在时序方面,二者也有很大相关。9个减法器在参阅块分频器模块的效果下,作业于一切的时钟周期里边,而累加比较器则是以减法器输出的信号作为累加原材料的,这就使得累加比较器也有必要从时钟的起始点就开端作业。确认运动矢量的规范是SAD最小值。也便是要经过比较9个累加成果,确认出最小值,并由地址计数器模块找到这个最小值所对应的运动矢量。

2.5 全体计划

全体计划主要是将三步查找法中的三步分隔进行。在外部输入信号的操控下,先输入第一步查找的地址核算操控因子,使得寻址规模是在步长为4的9个数据块群里边,第一步查找完结时将第一步查找到的最佳运动矢量输入到第二步的查找中,完结机制和第一步仅有的差异便是地址核算和发生的寻址规模不同,这样一直到完结第三步查找时,将第三步查找得到的最佳运动矢量作为当时块在这个查找窗口里边的最佳运动矢量。

3 、试验成果与剖析

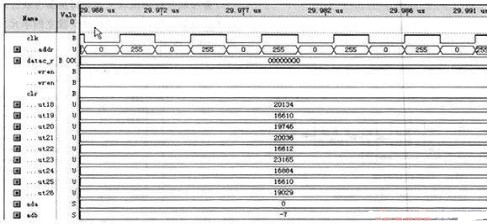

本规划选用StraTIx II系列的EP2S15F484C3器材进行仿真,仿真成果如图6所示。

由仿真成果可知整个查找进程彻底契合时序要求,总的逻辑资源占用率是27%。组合查找表运用了2 169个,占总数量12 480的17%。专用逻辑寄存器运用了2 855个,占总数量12 480的23%。而用的总的寄存器数也便是2 855。运用了180个片上引脚,占总个数的52%。运用了86 088比特的块存储器单元,占总的快存储器数量的21%。查找到的最佳运动矢量(0,-7),由前两步的查找成果可知其彻底正确。

4、 结束语

本文中选用FPGA规划的运动估量计划不管在查找速度,资源使用仍是时序操控上都具有必定的优越性,能够大大提高视频编码器规划的性价比。别的,跟着半导体工艺的不断进步,FPGA的性价比将不断提高,将使得运动估量甚至视频编码的技能不断提高。

责任编辑:gt