作者:A.Glascott-Jones, M. Wingender, N. Chantier, G. Thepaut, J.P Amblard, E. Marcelot, e2V公司

模数转化器(ADC)的运用在雷达和直接下变频接纳机等频域运用中正变得越来越遍及。对这些高频运用来说,动态规划和本底噪声特别重要,这也为12位ADC的推行供给了推动力。不需求外部下变频器就能直接发生传输信号和直接转化接纳信号的吸引力是很显着的,由于这种计划具有灵活性和元件数量削减的优势。关于元件面积和功耗等约束条件十分要害的航空和空间运用中这一点特别重要。

很长时刻以来这种没有混频器的直接变频一直是体系架构师朝思暮想的产品,现在跟着半导体技能的开展,咱们能够看到有许多商用元件能够用来在更多的运用中完成这种体系。本文评论了高频运用要获得最好功用所需的变频器特性,包含平整的频率响应、高输入带宽、低输入满刻度电压规划以及针对多阵列体系调整参数的才干。文章还评论了与挑选高分辨率高速ADC有关的体系规划考虑要素。

直接下变频架构

直接下变频接纳机在实践通讯体系和雷达运用中越来越遍及。比方通讯卫星中继器和组成孔径雷达地球观测体系等运用能够从完好的直接变频收发机的运用中收获颇丰。这种技能答应对整个脉冲式射频频谱进行直接数字化,进一步增强在一次快速傅里叶变换(FFT)扫描中能够观察到的感兴趣带宽,然后给接纳机功用带来更大的灵活性。在这种情况下,一个单路ADC就能够替换多个通道的传统中频(IF)下变频。

运用

L频段(1GHz到2GHz)有极好的气候穿透才干,因而它的运用十分多,包含通讯卫星中继器、组成孔径雷达(SAR)地球观测体系、军用空间监督、导弹检测和引导以及晴空对流层观测。

长途检测组成孔径雷达是一种十分风趣的运用,它运用天线与其方针区域之间的相对运动来履行地势成像。在这种运用中,高分辨率和高线性度以及准确调整采样点相位的才干很重要。电子战役(EW)体系要求高采样率、扫描尽或许和带宽相同宽的才干和低延时,以便快速捕获数据。

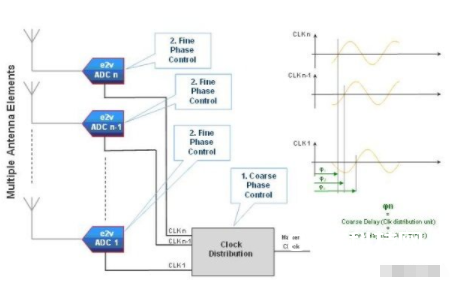

多阵列波束成形运用答应经过挑选方历来进步特定信号的增益,或许削减堵塞或搅扰信号的影响。在这种情况下,相位操控功用十分重要,如图1所示。

图1:天线阵列接纳机体系。

单内核ADC

关于在L频段运用中运用的ADC来说,有两个要害目标很重要,即频谱纯度和本底噪声。

频谱纯度:

真实的单内核架构具有很大的优势,由于它不需求内部替换就能到达1.5GS/s的更新速率。因而在扩展温度规划内作业之前或作业期间都无需校准。(替换型ADC的一个特点是具有显着的替换脉冲。偏移失配将发生一个固定频率的脉冲。但是,增益和相位失配将发生取决于输入信号频率的杂散频率。事实上,运用内部替换的ADC常常要求校准来防止由于增益、偏移和采样孔径延时的失配而引起的无杂散动态规划功用劣化。

从图2所示的频谱纯度图能够看到单内核的优势。频率的挑选要使主信号及其谐波在FFT图中紧靠在一起。这样能够使频谱其它部分自由地显现与任何其它非信号相关的杂散信号,比方时钟脉冲。替换式ADC或许能很好地在这个区域显现脉冲,但咱们能够看到,单内核具有无杂散区和90dBc的频谱纯度。

单内核架构在延时方面也有优势。例如,EV12AS200的延时能够低至3个时钟周期,这在电子战役和盯梢体系等运用中十分有用。

图2:EV12AS200的频谱纯度图。

本底噪声:

高带宽ADC的信噪比背面的因子能够由下列公式确认:

其间,nqi是抱负量化噪声q/√12,nqd是与抱负(DNL)的误差。nthermal是热白噪声,njitter是总的颤动值,由内部ADC颤动和外部时钟颤动组成。

假如内部时钟颤动大约为100fs rms,这意味着外部时钟的挑选应完成至少具有这个颤动值的体系,抱负情况下更小的颤动能够完成最佳的功用。下表给出了依据EV12AS200 ADC目标核算噪声功用的比方。

表1:典型的本底噪声核算。

L频段运用中别的一个重要的考虑要素是,一直到第二奈奎斯特区的结尾功用都应坚持稳定。这也暗示带宽应掩盖这个区域,并且比方SFDR、三阶互调指数和有效位数(ENOB)等功用参数应坚持平整(见图3)。

图3:EV12AS200的有效位数值。

ADC功用

鉴于多阵列规划是这种类型ADC的一种重要运用,ADC应该能够与阵列中的其它ADC匹配。因而增益、偏移和相位应具有调整功用。例如,下面描绘的功用是十分抱负的:

ADC增益操控:精调(±5%),运用10位DAC(±0.5 LSB)

ADC偏移操控:精调(±5%),运用10位DAC(±0.5 LSB)

ADC采样延时调整:30ps精调规划,10位DAC:30fs步距

这些功用还能用来替换多个12位ADC(用于添加实践采样率)。别的,在初始化过程中对齐多个通道的同步功用也很重要。这个功用还能够与触发功用同享,答应外部数字输入与模仿数据完成时刻上的同步。

由于输出数据速率将挨近内部FPGA的极限,一个重要功用是要能解复用(DMUX)这个数据,以引进更多输出端口的价值来下降数据速度。(EV12AS200供给1:2 DMUX解决计划)

别的一个重要功用是输入电压满刻度规划。ADC的谐波功用十分低,以致于输入驱动器上不良的杂散电平会严重影响体系功用。假如ADC能够承受低的输入电压,那么这个问题就能得以减轻。EV12AS200的输入电压规划是500mVpp。

规划考虑

时钟源和驱动体系的挑选很重要,由于颤动是核算总噪声的一个主要要素。要想获得最优功用,100fs左右的颤动是比较抱负的。这意味着源相位噪声为150dBc/Hz或以下,任何时钟缓冲器的附加颤动要远小于100fs。

PCB盯梢也是要害点,模仿盯梢应与源(或负载)匹配,才干获得挨近1的VSWR。数字盯梢应匹配到100Ω阻抗,长度也要匹配到好于±2.5mm,以保证接口FPGA的摆率误差不会太大。FPGA接口也是体系的一个杂乱部分。为了完成高数据速率,或许需求扩展运用内部的串行/解串(SERDES)单元。

体系功用

体系功用能够经过后处理和实时技能进一步增强,比方积分非线性(INL)校对和运用高频振荡(Dither)改进SFDR。

INL曲线形状对ADC的谐波功用有很大的影响。经过表征这个INL并运用接口FPGA中的查找表(LUT)能够最大极限地减小INL,然后进步SFDR功用。查找表校对是一种简略的减去或添加丈量编码得到的INL值。运用这种技能对FPGA的规划影响很小,对吞吐量没有影响。在许多情况下,添加用于INL校对的查找表能够进步SFDR功用10dB。

向输入数据中添加带外噪声源也能改进SFDR功用。这能够是简略的一个经过低通滤波后的噪声发生器,经过运用多端口变压器将它添加到输入信号中。作用是在ADC输入规划内移动输入信号,有利于削减INL效应,并进步SFDR(见图4)。

图4:运用高频振荡改进SFDR。

图4上半部分的频谱显现了没有附加颤动的谐波,下半部分图显现了带高频振荡的谐波,能够看出杂散谐波有显着减小。

关于作者

Andrew Glascott-Jones是坐落法国格勒诺布尔的e2v公司混合信号ASIC业务部运用工程师。Andrew在电子丈量体系规划范畴有近25年的丰厚经历,包含:精细丈量,粒子尺度调整,X射线成像和激光光谱学。e2v公司的混合信号ASIC业务部门主要为轿车、工业和医疗商场中的传感器接口运用规划和供给定制IC。Andrew担任e2v公司供给的开发套件,并在ASIC开发阶段向客户供给协助。这些套件供给了I.P.模块比方,有助于客户在规划周期前期展现概念验证,并高效的预先开发完好的ASIC。

责任编辑:gt