消费性电子产品汰换周期越来越短,且功用杂乱度不断进步,使得体系研制人员面对缩短产品开发时刻的严峻应战。所幸,如今主动化测验体系已开端导入开放式FPGA,将有助EDA开发环境与丈量软件的整合,让工程师可一起进行体系规划与测验,加快研制时程。

现在测验工程师所面对的最大应战之一,便是个人观念局限于现在的技能中而停滞不前,因而,本文特别供给技能趋势的相关常识,针对测验与丈量工业,评论足以影响整个工业的重要技能与办法。

规划与测验并行为大势所趋

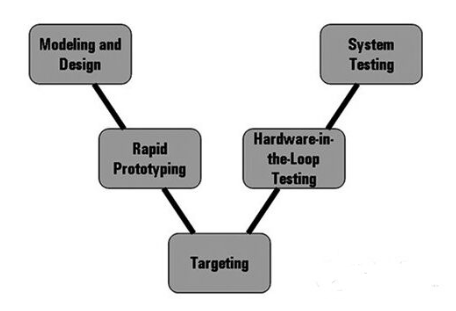

对现在的研制单位来说,缩短产品开发周期几乎是首要任务,特别是轿车与航空工业。要缩短开发时刻的办法之一,便是一起进行规划与测验,这样的产品开发形式常以“V-diagram”模型(图1)表明。这些工业的终究产品,往往构成高杂乱度“体系中的体系”;而V-diagram左面为“规划”,右边则为“测验”,其背面的概念,便是在开宣布完好体系之前,先开端测验、查验子体系以达更高功率。只需是需求高度监控环境的工业,就常见到如V- diagram 的同步规划/测验办法,并且现在已有其他类型的设备或工业逐渐选用相关实例。以半导体和消费性电子工业为例,其“时刻短的产品运用周期”与“不断进步的产品杂乱度”特性,都是缩短产品开发时刻的瓶颈。

图1 V-diagram产品开发模型

依据2009年麦肯锡(McKinsey)针对半导体工业规划的问卷研讨成果,半导体工业“产品生命周期”几乎是轿车工业的叁分之一罢了。另一份麦肯锡问卷研讨亦指出,半导体新产品规划的均匀开发时刻约为19个月,因而,研讨人员概括出“研制完好度(RD Excellence)”为加快开发时程的首要要害。

依据商业需求,产品开发进程有必要更注重研制完好度,因而电子工业已越来越趋向规划与测验并行。要强化此实例的首要办法,便是进步电子规划主动化(EDA)模仿软件与测验软件之间的联接。

进步EDA/测验软件联接

若要了解模仿软件在产品规划流程中的人物,有必要先了解软件在产品开发的“规划”与“测验”阶段有何效果。在初始的规划/模仿期间,EDA软件可针对模仿产品的物理或电子行为(Electrical Behavior)树立模型(图2)。EDA软件基本上归于公用程式,即依据一系列的输入,透过数学模型而出现受测物(DUT)的输出,再将相关衡量成果供给予规划工程师。

图2 软件于产品开发阶段所扮演的人物

在开发产品的查验/认证阶段,软件运用条件仅有少许不同,首要是能主动丈量实践的塬型即可。但查验/认证阶段所需的丈量演算法,亦与EDA软件东西所运用的演算法相同,这点则和规划/模仿阶段相似。

现在EDA软件正在开展中的功用,便是要于EDA环境与测验软件之间,进步软件联接功用的层级。更进一步解说,这种联接功用便是要让现有的EDA软件环境可驱动丈量软件,并且丈量主动化环境可主动联接EDA规划环境。

联接规划与测验软件环境的长处之一,即于规划程序的初期,软件即可供给更丰厚的丈量演算法。工程师不只可于规划初期进一步了解自己的规划,其模仿作业亦能整合查验/认证程序所获得的材料。第二项长处,则是让测验工程师在规划程序中,即可加快开发有用的测验程序代码,以利缩短杂乱产品的上市时刻。

透过EDA软件进行丈量 产品规划周期大幅缩短

EDA与测验软件联接而改进规划程序的办法,便是供给更丰厚的丈量功用。基本上,EDA东西将透过行为形式(Behavioral Model)猜测全新规划的行为。惋惜的是,固定形式的规划均是透过丈量原则进行查验,与查验终究产品所用的丈量原则大不相同,因而难以整合已模仿与已丈量的材料。现在业界正朝向“从规划到测验共用单一东西链”的一条鞭办法,让工程师可早将丈量作业带入规划流程。

明导世界(Mentor Graphics)副总裁兼体系层级工程部门经理Serge Leef表明,在联接EDA东西与测验软件之后,工程师可于产品开发期间一起规划测验工作台,并于规划程序中早获得测验报告。因为工程师能一起进行开发与测验成果,而不是像曾经有必要依序完结作业,因而能大幅缩短规划周期。

先以举动电话的多重形式射频(RF)功率放大器(PA)为例,此类元件的传统规划办法,即运用如AWR Microwave Office的RF EDA东西。透过EDA环境,工程师可透过模仿作业而获得RF特性参数,如功率、增益、1dB紧缩点(Compression Point)等,但终究产品一切必要满意的RF丈量原则,却又是专为举动电话规范(如全球举动通讯体系/增强数据率演进(GSM/EDGE)、宽频分码多工 (WCDMA)、长程演进计画(LTE))所树立。

在此之前,因为丈量杂乱度的不同,往往须实践丈量DUT,才干透过衡量规范(如LTE过错向量起伏(EVM)与附近通道漏比(ACLR))的“规范标准”而获得丈量材料。但现在因为EDA软件与主动化软件可联接,让工程师可于模仿设备上建构EDA环境,从而运用完好的丈量演算法。也因为如此,工程师在规划初期即可找出杂乱产品或体系相关的问题,亦等于缩短规划时刻。

行为模型助力 规划/丈量一起进行

在整合规划与测验实例的第二个趋势,便是运用EDA所发生的行为模型,加快开发产品查验/认证,并u作测验软件。在此之前,让产品规划程序功率失落的塬因之一,便是特定产品的测验程序代码开发缓慢,乃至要比及初次测验实体塬型之后。不论是特性描绘或出产测验程序代码,若要能加快开发程序,最好透过软件u作既定规划的塬型并直接做为DUT。透过此办法,工程师将可以于产品规划期间一起,开发特性描绘与出产测验软件,从而加快上市时刻。

以美敦力(Medtronic)为例,该公司最近就针对心率调节器开发而选用此规划办法。美敦力透过特别规划的新软件套件联接EDA环境与丈量软件,联接软件环境之后,工程师可于u作实践硬件之前就开宣布测验工作台,而透过此规划办法而到达的平行机制,让工程师能因而加快产品上市时刻。

在进步工程规划完好度的进程中,整合“规划实例”与“测验实例”的重要度将越来越被突显。因为EDA与丈量软件间越来越严密,工程师将能于未来数年之内更有用运用EDA软件,以获得更完好的模仿作业,并让EDA模仿功用强化查验与出产测验的程序。

FPGA发动下代代丈量仪器改造

曩昔20多年来,“微处理器架构、可由运用者规划程式的丈量演算法”已成干流概念,让测验体系可敏捷承受不断变化的客u化测验需求。此办法亦即所谓的虚拟仪控,且供货商亦持续设法规划其他仪器优势–更高效能、进步客u化程度、更广泛选用现成技能、下降测验体系本钱等。

如果说微处理器带动虚拟仪控的改造,那么现场可编程闸阵列(FPGA)就又发动了下个阶段。FPGA用于仪器之中已有数年,举例来说,现在高频宽示波器虽可L集很多材料,但运用者并无法敏捷剖析一切材料。这些设备上的硬件界说演算法一般均建置于FPGA,以履行材料剖析与减缩(均匀、触发、波形数学)、运算计算(均匀值、规范差、最大值、最小值)、处理材料以利显现,最终为运用者出现有意义的成果。这些功用尽管确有其价值,但却无法突显FPGA潜在功用,在大部分条件下,运用者并无法将客u化丈量演算法布置至FPGA。

丈量硬件上的开放式FPGA,可为仅有处理器的体系供给多项优势。依据FPGA的强壮运算功用,将可到达更高的测验传输率与更广的测验围,从而缩短测验时刻并下降出本钱钱。微处理器所无法到达的测验作业,亦可透过FPGA的低推迟特性而建置。FPGA既有的平行机制,可到达真实的多履行序测验,乃至逾越多中心处理器。在即时测验的硬件排序与待测物操控程序中,FPGA更扮演要害人物。

由工业研讨公司Frost Sullivan所宣布的2011年模组化仪控商场研讨指出,由Altera与赛灵思(Xilinx)等公司对FPGA功用的进步,将对测验与丈量运用影响深远,对需求高精确度与快速处理功用的客户而言尤为如此,现在商场上有越来越多的开放式FPGA产品。

尽管市面上已有许多硬件可供挑选,但大多数的丈量演算法都是针对虚拟仪控的微处理器部分所开发。依据材料形状、程式规划模型、特定硬件特点(如时序约束) 等的不同,并无法简略移至FPGA持续运用。厂商要开发专业且安稳的FPGA丈量硅智财(IP)须具有专业常识并耗上很多时刻,因而,现在仪控硬件中的大多数FPGA仅运用供货商界说的固定演算法,无法由运用者自行规划程式。

2011年业界就现已开端评论异质运算(Heterogeneous Computing),意行将演算法分配至多种运算架构(中央处理器(CPU)、图形处理器(GPU)、FPGA、云端体系)中,找出最佳的演算法建构资源。除硬件架构自身的强壮功用考量之外,异质运算代表各种体系的程式规划难题,且丈量演算法难以在体系之间“带着”,杂乱度的确有所影响。

业界最近针对测验工程领导厂商的全球查询指出,约有54%受访者以为未来技能开展将可进步测验传输率并下降体系本钱,从而缩短开发时刻。为战胜此难题,工业界正活跃开发相关东西,以期能跨硬件体系运用演算法,并且让FPGA可遍及于测验体系。

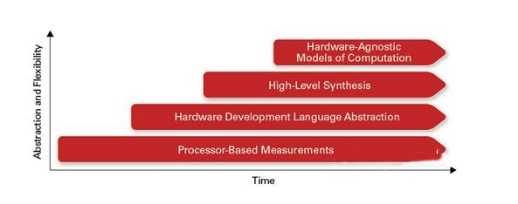

此种跨硬件的体系将可供给硬件描绘言语(HDL)抽象化。HDL是以文字办法描绘逻辑闸层(Gate)与信号层(Signal-level)的行为,而 HDL抽象化(Abstraction)东西则透过图形或简图的出现办法,撷取更高层级的规划(图3)。与HDL相较,尽管这些东西的确下降FPGA技能的门槛,但仍无法彻底省掉某些FPGA规划的特定硬件特点,如资源分配、数位信号处理器(DSP)切割架构、管线流转(Pipelining)、内建记忆体(On-chip Memory)等。在这些情况下,仍须从头规划/查验演算法才干联接FPGA,也促进开发东西的未来开展。

图3 开发软件有必要能跨履行体系,而到达更高的硬件抽象化与灵敏度,以达更高效能、更高本钱效益,且更能敏捷上市。

挟多重优势 开放式FPGA遍及于丈量体系

高阶组成(High-level Synthesis, HLS)东西可于较高阶级撷取演算法,并为既有建置独立分配其效能特点,如推迟、时脉率、传输率、资源运用等。因为特别建置并不归于演算法界说,如此也下降演算法的可携性。此外,开发工程师在规划硬件特性(管线流转、资源裁定等)时,并不须顾忌特定硬件。HLS的概念已存在超越20年,但市面上的东西是最近才渐趋老练。这些东西的确供给相关优势,但仅针对FPGA或特定运用积体电路(AS%&&&&&%),并未归入如GPU与微处理器的其他运算渠道。为打破这些 HLS东西的约束,业界供给测验版软件,整合既有的LabVIEW材料流程式图与HLS长处,以因应FPGA规划作业。如此一来,建置FPGA亦可归入很多LabVIEW丈量与操控演算法,而不受制于微处理器的履行情况,亦不须针对FPGA布置作业而从头规划很多演算法。此软件现在仍在测验中而无法遍及,但最终的方针成果可期。

立异开发东西的最终一步,便是让跨硬件体系整合运算/规划的多种模型。这些运算模型包括LabVIEW材料流程式图、DSP简图可用于RF与通讯运用中的多重速率信号处理、文字式数学可撷取类教科书的方程式、状况机器用于数位逻辑与协议等。

举例来说,如赛灵思Zynq可延伸处理渠道所建构的体系单芯片(SoC)体系,未来将整合双中心安谋世界(ARM)微处理器与FPGA。此芯片具有极高的异质运算潜力,但因为微处理器与FPGA别离需求不同的运算言语/模型,所以程式规划作业的难度极高。在抱负状况下,工程师应具有多样的运算模型以援助一切体系,并以更有用的办法撷取演算法,最终布置至最佳履行体系。依据事务需求的不同,这e的“最佳”或许代表最高效能、最高本钱效益,或最短上市时刻。若要让东西调配非特定硬件的运算模型,仍有一段开发的路要走,并且有必要能满意现在测验体系的开发需求。

开发软件有必要能跨履行体系,而到达更高的硬件抽象化与灵敏度,以达更高效能、更高本钱效益,且更能敏捷上市。

尽管非特定硬件的丈量演算法与高阶组成东西没有提高干流,但开放式FPGA正逐渐遍及于主动化测验体系中。FPGA在测验作业中的优势,已值得许多厂商投入更多开发本钱,并且只需进步软件东西,将连带缩短开发时刻并下降杂乱度,促进更多相关运用。好像微处理器与相关 的软件开发环境/丈量演算法,带动了虚拟仪控的改造,运用者可规划的FPGA亦将带动图形化体系规划(GSD)的下一波改造,催生未来的测验体系。