10.4运用FPGA完成常用显现接口(DisplayInterface)

10.4.1七段数码显现接口的规划与完成

七段数码管因为价格低廉,运用简略,常常被用来完成一些简略的状况显现功用。七段数码管的规范外观图如图10.16所示。右下角的圆点用Dp来表明,用来完成小数点的显现。

七段数码管常常用来显现十进制或十六进制的数,所以在数据显现之前,首先要进行二进制到十进制或许十六进制的转化。将它们转化成十进制的或是十六进制的数。

七段数码管分为共阴和共阳两种类型。比方,赤色飓风开发板运用的是共阴类型的数码管,信号是高电平有用。十六进制数据在显现的时分对应的各段输出对应联系如表10.2所示。

表10.2 十六进制数据与输出的映射联系

|

数据 |

a |

b |

c |

d |

e |

f |

g |

Dp |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

|

2 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

|

3 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

|

4 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

|

5 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

|

6 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

|

7 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

|

8 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

9 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

|

A |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

|

B |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

|

C |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

|

D |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

|

E |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

F |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

赤色飓风开发板上选用的是4位并联的数码管。4个数码管共用8条数据线,操控线是独立的。假如4个数码管要显现不同的数值,比方显现1234,那么就需求选用一种操控战略。最常用的办法便是动态扫描显现。

动态扫描显现运用了时分的原理和人的视觉暂留效应。例如,一个4位动态扫描数码显现器的显现周期可划分为4个阶段。

阶段1→阶段2→阶段3→阶段4

每个周期只选通一位数据。在周期1显现第一个数码,周期2显现第二个数码。在扫描4个阶段后,又从头按次序循环。假如扫描的速度足够快,从视觉上看就好像4个数码管一起显现不同的内容。

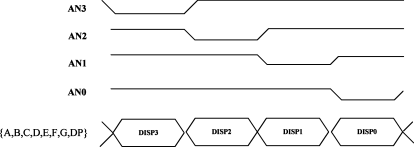

4位扫描数码管共有4组BCD码(4位)输入线,8根8段译码输出线和4根位选通线。扫描工作中,先从4组BCD数据中选出一组,经过BCD/7段译码器译码后输出。与此一起,3/8译码器产生位选通信号,则在此瞬间,数码管应该为要显现的数值。然后再选出下一组数据译码后输出,位选通信号则相应下移一位,将下一数码管选通输出,如图10.17所示。

图10.17动态扫描原理示意图

10.4.2字符型LCD显现接口的规划与完成

液晶屏(LCD)一般分为点阵型和字符型两种。字符型的液晶屏相关于数码管来说,能够显现更多的内容和字符,人机界面更为友爱,并且操作简略,因而得到了广泛的使用。不同厂家的字符型LCD尽管类型不同,可是操作办法基本是共同的。

字符型LCD一般会依据显现字符的数量来确认类型,如1602表明这个液晶能够显现2行字符,每行为16个。赤色飓风开发板上选用的字符型LCD的类型便是1602。下面就以1602为例来介绍字符型LCD显现接口的规划办法。

1602型液晶模块选用14针规范接口,各个管脚的界说如表10.3所示。

表10.3 1602型液晶模块的管脚装备表

|

管脚 |

符号 |

阐明 |

|

1 |

VSS |

器材地 |

|

2 |

VDD |

+5V电源 |

|

3 |

V0 |

对比度调整端,接正电源时对比度最弱,接地电源时对比度最高,对比度过高时会产生“鬼影”,运用时能够经过一个10kW的电位器调整对比度 |

|

4 |

RS |

寄存器挑选,高电平时挑选数据寄存器,低电平时挑选指令寄存器 |

|

5 |

RW |

读写信号线,高电平时进行读操作,低电平时进行写操作。当RS和RW共同为低电平时能够写入指令或许显现地址,当RS为低电平、RW为高电平时能够读忙信号,当RS为高电平、RW为低电平时能够写入数据 |

|

6 |

E |

使能端,当E端由高电平跳变成低电平时,液晶模块执行指令 |

|

7~14 |

D0~D7 |

8位双向数据线 |

1602液晶模块内部的字符产生存储器(CGROM)现已存储了160个不同的点阵字符图形。这些字符包含:阿拉伯数字、英文字母的大小写、常用的符号和日文化名等。每一个字符都有一个固定的代码,比方大写的英文字母“A”的代码是0100_0001B(41H)。

显现的时分,模块把地址41H中的点阵字符图形显现出来,咱们就能看到字母“A”。在编程实时,只需求输入相应字符的地址,液晶屏就会输出相应的字符。

FPGA对液晶模块的写操作、屏幕和光标的操作都是经过指令编程来完成的。1602型液晶的操作指令表如表10.4所示。

表10.4 1602型液晶模块的指令表

|

序号 |

指令 |

RS |

RW |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

1 |

清显现 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

2 |

光标回来 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

* |

|

3 |

光标或显现形式 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

I/D |

S |

|

4 |

显现开/关操控 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

D |

C |

B |

|

5 |

光标或字符移位 |

0 |

0 |

0 |

0 |

0 |

1 |

S/C |

R/L |

* |

* |

|

6 |

功用设置指令 |

0 |

0 |

0 |

0 |

0 |

DL |

N |

F |

* |

* |

|

7 |

字符产生器地址设置 |

0 |

0 |

0 |

1 |

字符产生器地址(AGG) |

|||||

|

8 |

DDRAM地址设置 |

0 |

0 |

1 |

显现数据存储器DDRAM的地址(ADD) |

||||||

|

9 |

读忙标志或地址 |

0 |

1 |

BF |

计数器地址(AC) |

||||||

|

10 |

写数据到RAM |

1 |

0 |

要写的数据 |

|||||||

|

11 |

从RAM读数据 |

1 |

1 |

读出的数据 |

|||||||

各条指令的阐明如下(表10.4中,设1为高电平、0为低电平)。

·指令1:清显现,指令码01H,光标复位到地址00H方位。

·指令2:光标回来,光标回来到地址00H。

·指令3:光标和显现形式设置。其间I/D表明光标移动方向,高电平右移,低电平左移;S表明屏幕上一切文字是否左移或许右移,高电平表明有用,低电平则无效。

·指令4:显现开/关操控。其间D表明操控全体显现的开与关,高电平表明开显现,低电平表明关显现;C表明操控光标的开与关,高电平表明有光标,低电平表明无光标;B表明操控光标是否闪耀,高电平闪耀,低电平不闪耀。

·指令5:光标或显现移位。其间S/C表明高电平时移动显现的文字,低电平时移动光标;R/L表明文字或光标的移动方向,高电平为右移,低电平为左移。

·指令6:功用设置指令。其间DL表明高电平时为4位总线,低电平时为8位总线;N表明低电平时为单行显现,高电平时双行显现;F表明低电平时显现5×7的点阵字符,高电平时显现5×10的点阵字符。

·指令7:字符产生器RAM地址设置。

·指令8:DDRAM地址设置。

·指令9:读忙信号和光标地址。其间BF表明忙标志位,高电平表明忙,此刻模块不能接纳指令或许数据,假如为低电平表明不忙。

·指令10:写数据。

·指令11:读数据。

10.4.3VGA显现接口的规划与完成

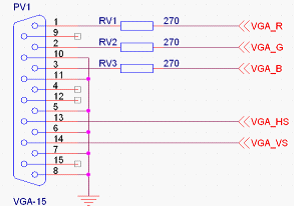

因为VGA接口是模仿信号,而FPGA只能支撑数字信号,因而需求专用的D/A转化芯片来完成模仿到数字的转化。常用的DAC芯片有ADI公司的ADV7123或许ADV7125等。

在某些使用场合下,VGA显现器仅仅是用来显现文字符号或许简略图形,不需求丰厚的色彩和细腻的画面。这时分,VGA接口就能够适当地简化。

规范的VGA接口衔接器为DB15,在15个管脚里边有5个是最重要的。它们分别是红、绿,蓝三基色信号和水平、笔直两个同步操控信号,如图10.18所示,其间,VGA_R、VGA_G、VGA_B、VGA_HS、VGA_VS是直接衔接到FPGA的管脚。

图10.18简化的VGA接口电路衔接

FPGA的管脚只要高电平和低电平两种状况,因而关于每个色彩重量信号也仅有两种状况。这样3个色彩重量就能够组合出8种色彩,如表10.5所示。

表10.5 简化的VGA接口色彩对照表

|

VGA_R |

VGA_G |

VGA_B |

对应的显现色彩 |

|

0 |

0 |

0 |

黑色 |

|

0 |

0 |

1 |

绿色 |

|

0 |

1 |

0 |

蓝色 |

|

0 |

1 |

1 |

蓝绿色 |

|

1 |

0 |

0 |

赤色 |

|

1 |

0 |

1 |

品赤色 |

|

1 |

1 |

0 |

黄色 |

|

1 |

1 |

1 |

白色 |

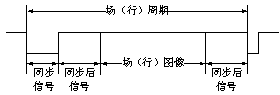

VGA信号假如要正常显现,那么输出信号有必要满意必定的时序联系。如图10.19所示为VGA接口电路的通用时序联系。不同的分辨率和刷新率有不同的时序如表10.6所示。

图10.19VGA接口电路的通用时序联系

表10.6 常见分辨率的VGA时序参数表

|

显现形式 |

像素时钟 /MHz |

水平方向(以像素核算) |

笔直方向(以行核算) |

||||||

|

有用视频信号 |

同步前 |

同步信号 |

同步后 |

有用视频信号 |

同步前 |

同步信号 |

同步后 |

||

|

640×48060Hz |

25.175 |

640 |

16 |

96 |

48 |

480 |

11 |

2 |

31 |

|

800×60060Hz |

40.000 |

800 |

40 |

128 |

88 |

600 |

1 |

4 |

23 |

|

1024×76860Hz |

65.000 |

1024 |

24 |

136 |

160 |

768 |

3 |

6 |

29 |